Please Check for CHANGE INFORMATION at the Rear of this Manual

# 4024 AND 4025 COMPUTER DISPLAY TERMINALS

(Vol. 1, Theory of Operation)

SERVICE MANUAL

Tektronix, Inc.

P.O. Box 500

Beaverton, Oregon 97077

MANUAL PART NO. 070-2830-00

PRODUCT GROUP 11

# WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

Copyright © 1979 by Tektronix, Inc., Beaverton, Oregon. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without permission of Tektronix, Inc.

This instrument, in whole or in part, may be protected by one or more U.S. or foreign patents or patent applications. Information provided on request by Tektronix, Inc., P.O. Box 500, Beaverton, Oregon 97077.

TEKTRONIX is a registered trademark of Tektronix, Inc.

Portions of this manual are reprinted with permission of Motorola, Inc., Carol Stream, Illinois 60187.

# **MANUAL REVISION STATUS**

**PRODUCT:** 4024 and 4025 Computer Display Terminals

This manual supports the following versions of this product: \[ \begin{cases} 4024 - B010100 and up \\ 4025 - B010100 and up \end{cases} \]

| REV. | DATE     | DESCRIPTION                                  |

|------|----------|----------------------------------------------|

|      |          | DECOM HOW                                    |

| @    | AUG 1979 | Original Issue                               |

| Α    | SEP 1979 | Revised: pages 2-2, 5-13, 5-14.              |

| Α    | FEB 1980 | Revised: pages 1-2, 12-7, Tab A, A-14, I-31. |

| Α    | MAR 1980 | Revised: page 9-39.                          |

|      | OCT 1980 | Revised: pages 3-1, 3-2 and 3-11.            |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

|      |          |                                              |

# CONTENTS

| Section 1 | INTRODUCTION                                       |

|-----------|----------------------------------------------------|

|           | About This Manual1-1                               |

|           | About the Terminals                                |

|           | Basic Characteristics                              |

|           | Differences Between 4024 and 40251-2               |

|           | Options                                            |

|           | Accessories1-4                                     |

| Section 2 | SYSTEM OVERVIEW                                    |

|           | Memory Address Space2-4                            |

|           | System RAM2-6                                      |

|           | Battery RAM                                        |

|           | I/O Address                                        |

|           | Fix-It ROM2-6                                      |

|           | Second Fix-It ROM2-7                               |

|           | System Firmware2-7                                 |

|           | Optional Firmware2-7                               |

|           | Display Memory2-7                                  |

|           | How Text is Stored and Displayed                   |

|           | Display List                                       |

|           | Tracker2-8                                         |

|           | Display Controller2-8                              |

|           | Entering Text from the Keyboard                    |

|           | Virtual Bit Map Graphics                           |

| Section 3 | VIDEO DISPLAY UNIT, POWER SUPPLY, AND MOTHER BOARD |

|           | Video Display Unit                                 |

|           | Display Power Supply                               |

| •         | Video Amplifier                                    |

|           | Horizontal Sync Amplifier                          |

|           | Phase Detector                                     |

|           | Horizontal Oscillator                              |

|           | Horizontal Pulse Shaper and Driver                 |

|           | Horizontal Output                                  |

|           | Vertical Sync Amplifier                            |

|           | Sync Shaper                                        |

|           | Vertical Oscillator3-9                             |

|           | Vertical Driver                                    |

|           | Vertical Output3-10                                |

| Section 3 (cont) | Terminal Power Supply3-12                  |

|------------------|--------------------------------------------|

|                  | Primary Windings                           |

|                  | Power Fail Detector3-12                    |

|                  | + 12 Volt Supply                           |

|                  | + 5.1 Volt Supply3-13                      |

|                  | -12 Volt Supply                            |

|                  | -5 Volt Supply3-13                         |

|                  | Mother Board3-14                           |

|                  | Signal Lines                               |

| Section 4        | KEYBOARD                                   |

|                  | Key Scanner 4-1                            |

|                  | Lights and Bell                            |

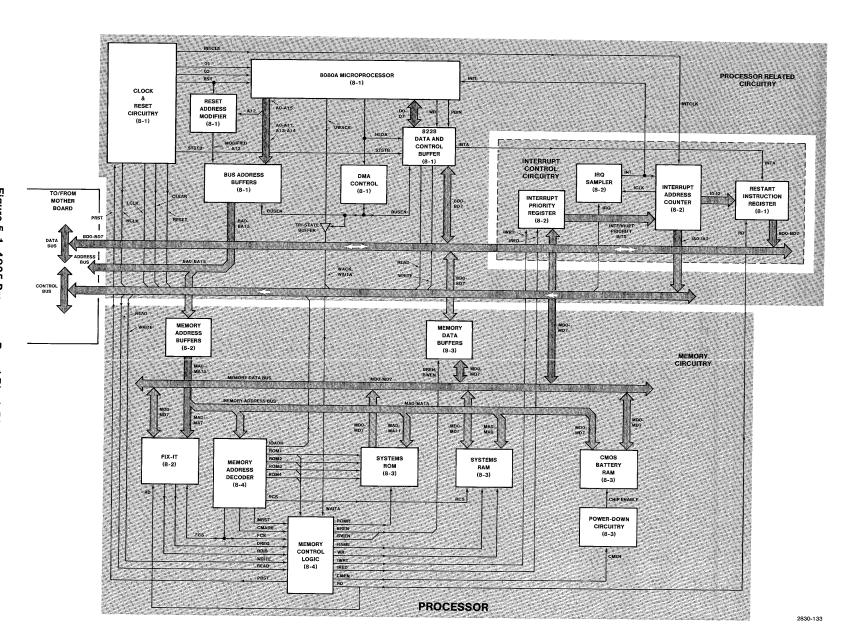

| Section 5        | 4025 PROCESSOR BOARD                       |

|                  | Introduction                               |

|                  | Comparison of 4024 and 4025 Processors 5-1 |

|                  | 4025 Processor Board Contents 5-2          |

|                  | Processor and Associated Circuitry5-4      |

|                  | 8080A Microprocessor                       |

|                  | Reset Address Modifier5-6                  |

|                  | Bus Address Buffers 5-7                    |

|                  | Clock and Reset Circuitry5-8               |

|                  | Data and Control Buffer5-9                 |

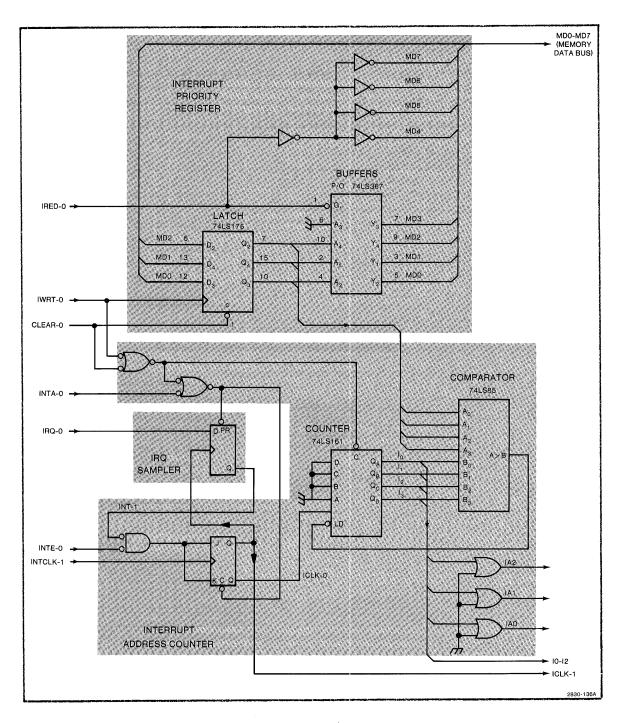

|                  | Interrupt Control                          |

|                  | DMA Control                                |

|                  | 4025 Processor Board Memory Circuitry5-16  |

|                  | Memory Address Buffers5-16                 |

|                  | Fix-lt 5-16                                |

|                  | System ROM5-18                             |

|                  | System RAM5-18                             |

|                  | CMOS Battery RAM5-19                       |

|                  | Power Down Circuitry5-19                   |

|                  | Memory Data Buffers5-19                    |

|                  | Memory Address Decoder 5-20                |

|                  | Memory Control Logic 5-22                  |

|                  | Connectors 5-25                            |

| Section 6 | 4025 COMMUNICATIONS INTERFACE BOARD                            |

|-----------|----------------------------------------------------------------|

|           | Introduction                                                   |

|           | Host and Keyboard Ports 6-1                                    |

|           | I/O Registers6-1                                               |

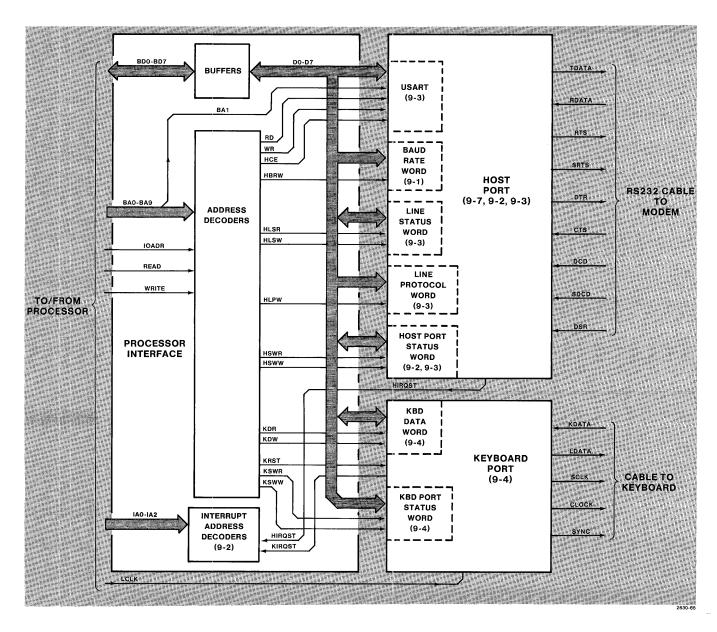

|           | Block Diagram6-6                                               |

|           | Processor Interface6-8                                         |

|           | Data Buffers                                                   |

|           | Address Decoders 6-8                                           |

|           | Interrupt Address Decoders6-9                                  |

|           | Host Port6-10                                                  |

|           | Introduction 6-10                                              |

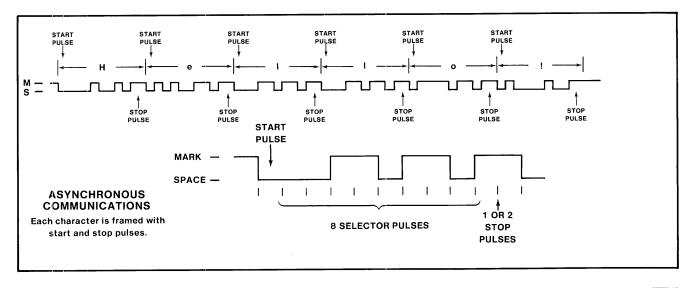

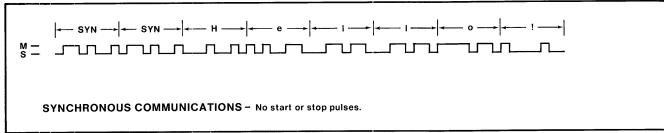

|           | Data Communications Overview6-10                               |

|           | Host Port Firmware6-15                                         |

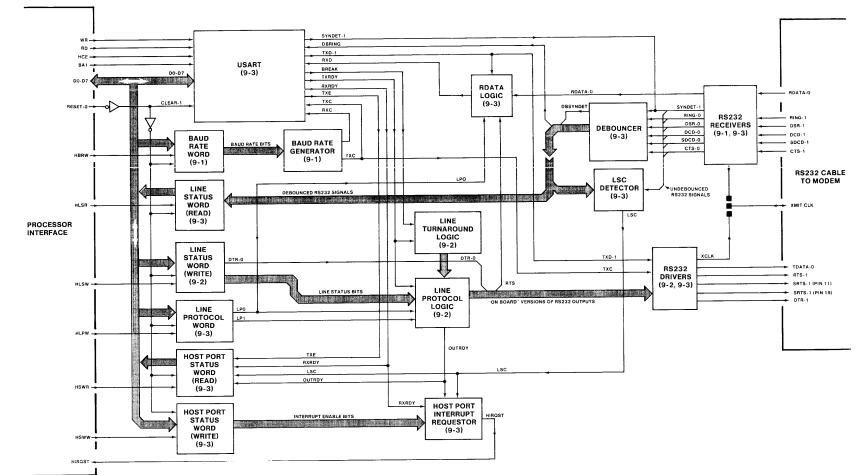

|           | Host Port Circuitry 6-17                                       |

|           | Keyboard Port6-34                                              |

|           | Introduction 6-34                                              |

|           | Keyboard Port Firmware6-34                                     |

|           | Keyboard Port Circuitry 6-35                                   |

|           | ,                                                              |

| Section 7 | 4024 PROCESSOR/COMMUNICATIONS BOARD                            |

|           | Introduction                                                   |

|           | Processor-Related Circuitry7-1                                 |

|           | Microprocessor                                                 |

|           | Clock and Reset Circuitry7-3                                   |

|           | Memory Address Buffers                                         |

|           | Bus Address Buffers                                            |

|           | Data and Control Buffer7-4                                     |

|           | Memory Data Buffers7-4                                         |

|           | Memory Map and I/O Address Decoders                            |

|           | Processor/Communications Board Memory Map                      |

|           | I/O Address Decoders                                           |

|           | ROM Circuitry                                                  |

|           | ROM Address Decoder                                            |

|           | ROMs                                                           |

|           | Fix-lt                                                         |

|           | Host Port Circuitry7-11                                        |

|           | USART                                                          |

|           | Baud Rate Generator7-11                                        |

|           | RS-232 Receiver and Drivers                                    |

|           | Host Port Status Word (Write)                                  |

|           | Host Port Interrupt Requestor                                  |

|           | IRQ Driver                                                     |

|           | Host Port Status Word (Read)                                   |

|           | Keyboard Port Circuitry                                        |

|           | 1.0, 200 a 1 of Onoundy 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |

iv

| DISPLAY MEMORY BOARD                                         |

|--------------------------------------------------------------|

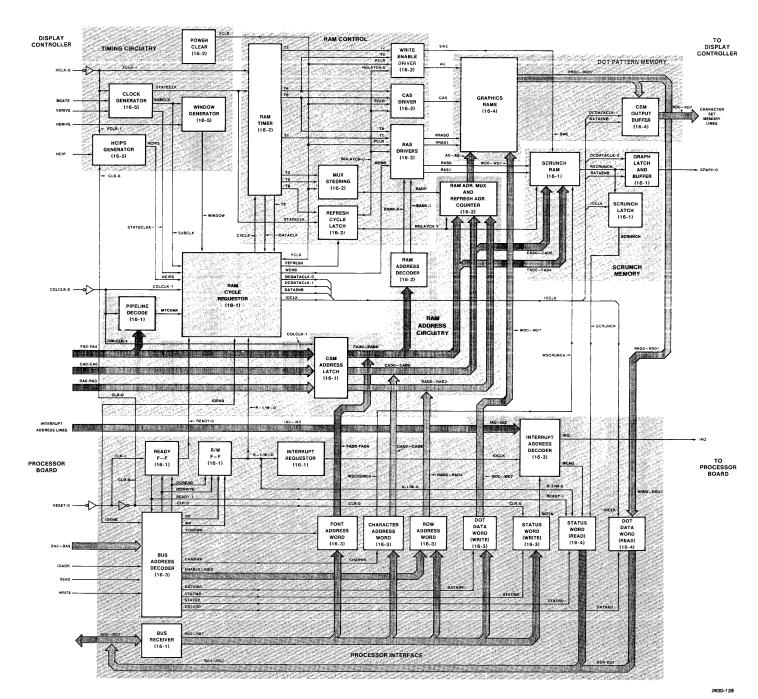

| Display Memory Board Concepts 8-1                            |

| Display Memory8-1                                            |

| Display List                                                 |

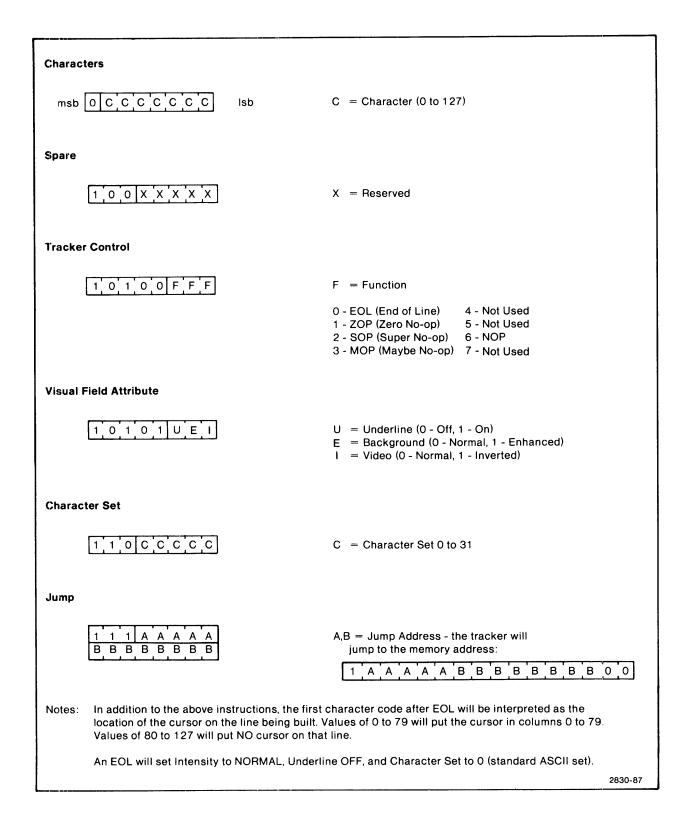

| Tracker8-2                                                   |

| Input and Output8-2                                          |

| Circuit Descriptions8-3                                      |

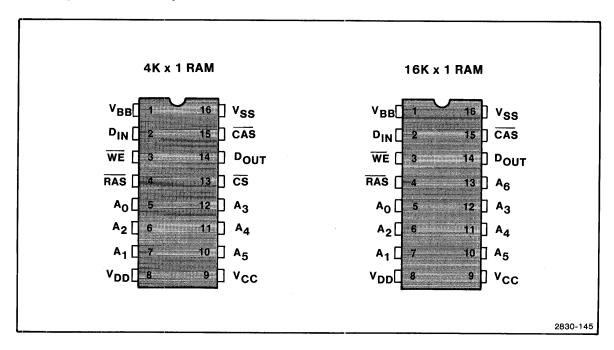

| Display RAM8-3                                               |

| RAM Controller8-5                                            |

| RAM Address Steering 8-10                                    |

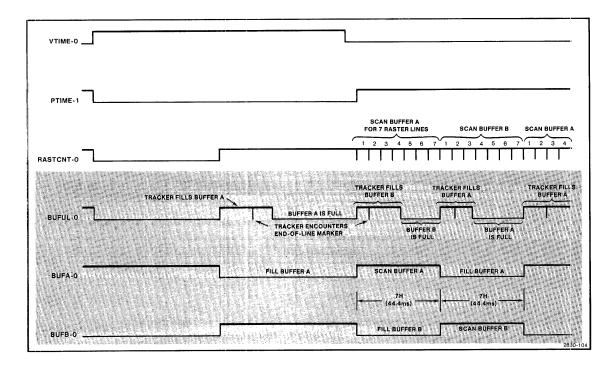

| Tracker8-11                                                  |

| Bus Interface Circuitry 8-17                                 |

| DISPLAY CONTROLLERS                                          |

| Introduction                                                 |

| Display Controller Concepts9-2                               |

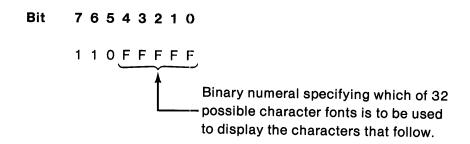

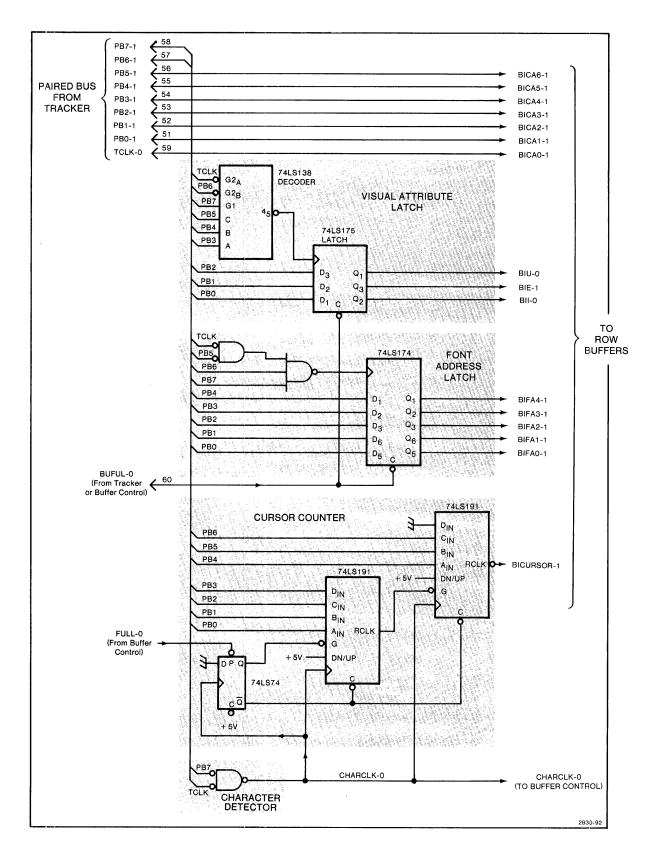

| Information from the Paired Bus9-2                           |

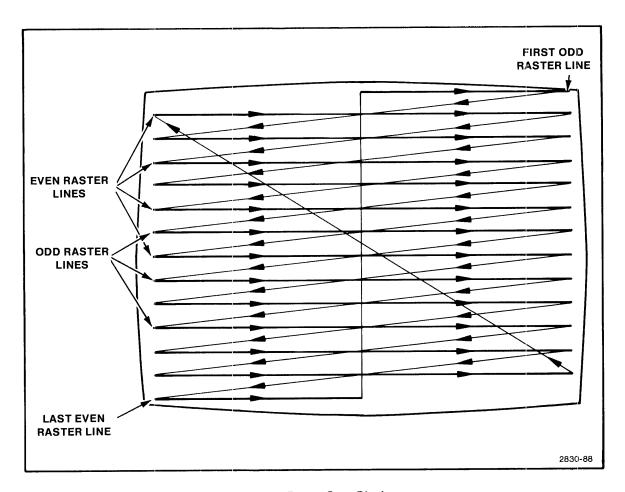

| Raster Scan Display9-4                                       |

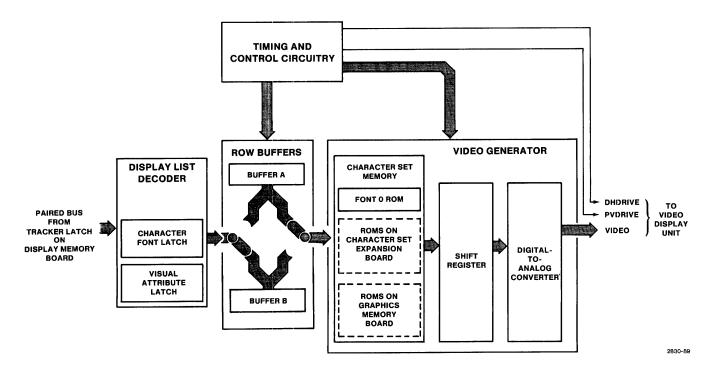

| Simplified Block Diagram9-5                                  |

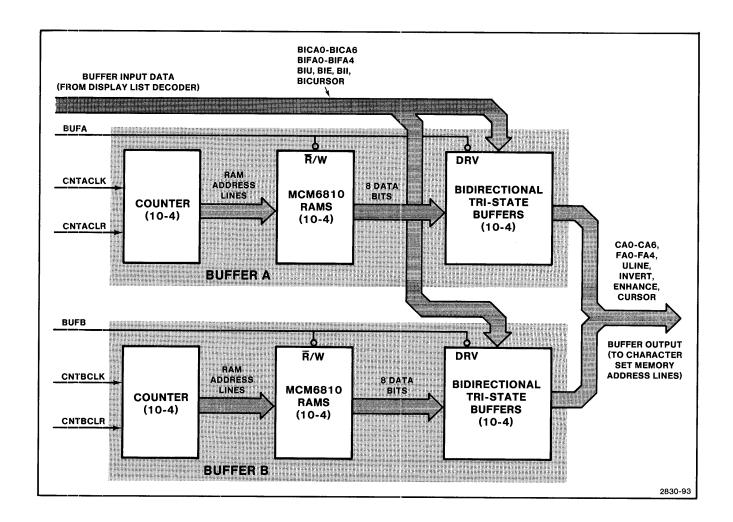

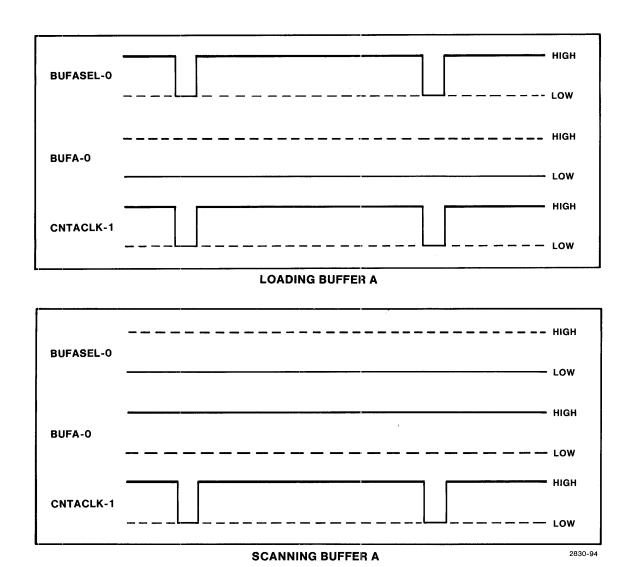

| Row Buffers 9-5                                              |

| Display List Decoder 9-6                                     |

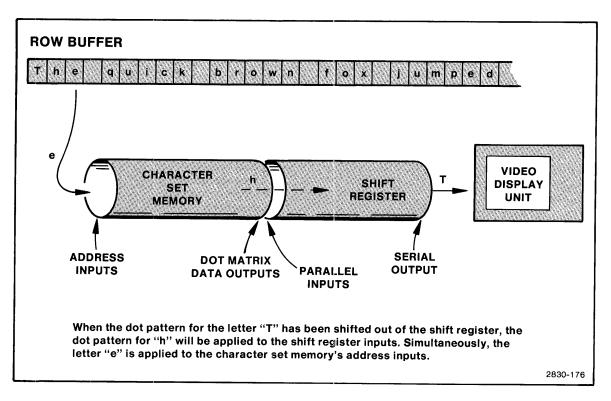

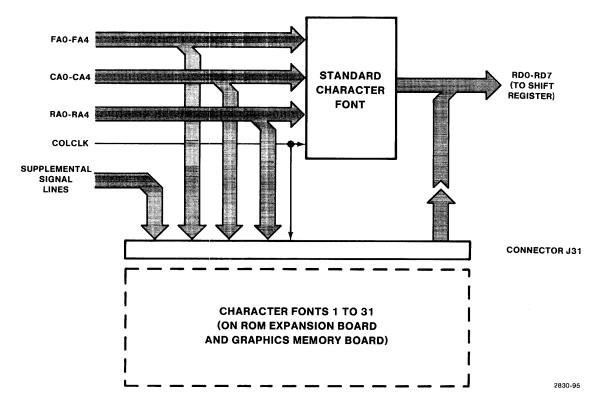

| Video Generator9-7                                           |

| Differences Between the Display Controllers9-10              |

| 4025 Display Controller9-11                                  |

| Display List Decoder 9-11                                    |

| 4025 Row Buffers9-16                                         |

| Video Generator9-19                                          |

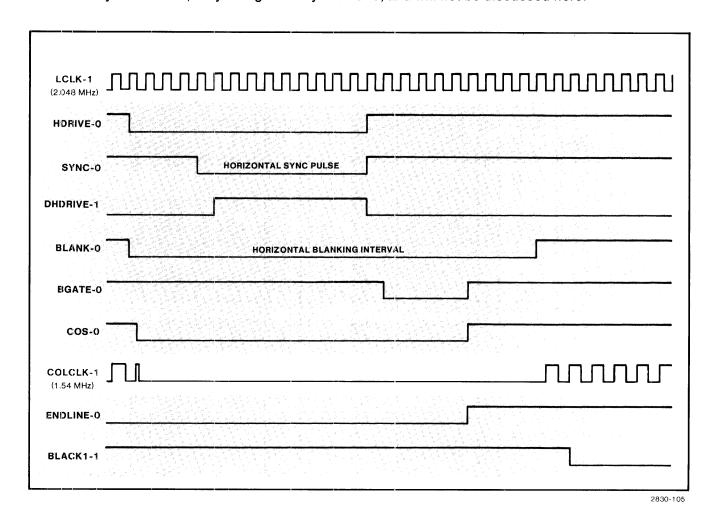

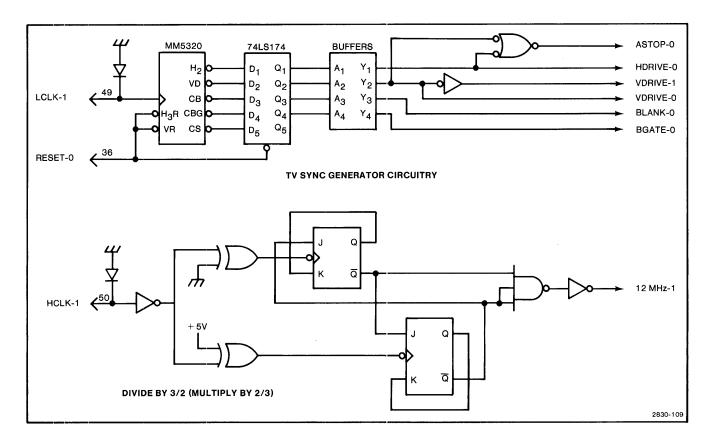

| Timing and Control Signals9-31                               |

| Timing and Control Circuitry                                 |

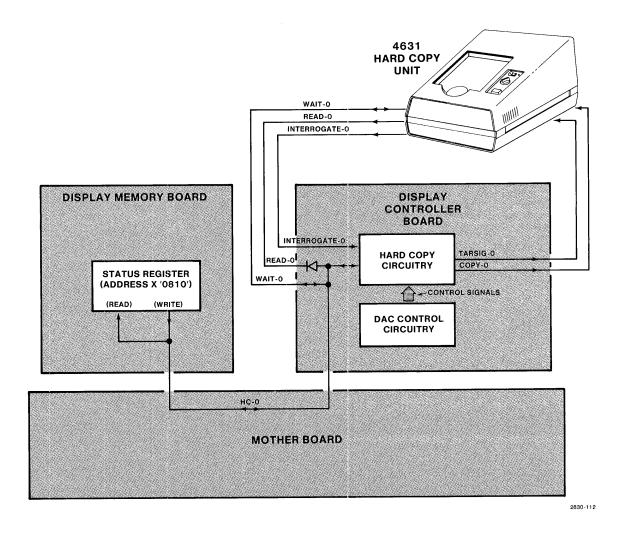

| Making Hard Copies9-46                                       |

| 4024 Display Controller9-54                                  |

| Block Diagram9-54                                            |

| Timing and Control Circuitry                                 |

| Display List Decoder 9-56                                    |

| Row Buffers                                                  |

| Video Generator9-56                                          |

| OPTION 1 HALF DUPLEX (4025 ONLY)                             |

| OPTION 2 CURRENT LOOP INTERFACE (4024 AND 4025) Introduction |

|                                                              |

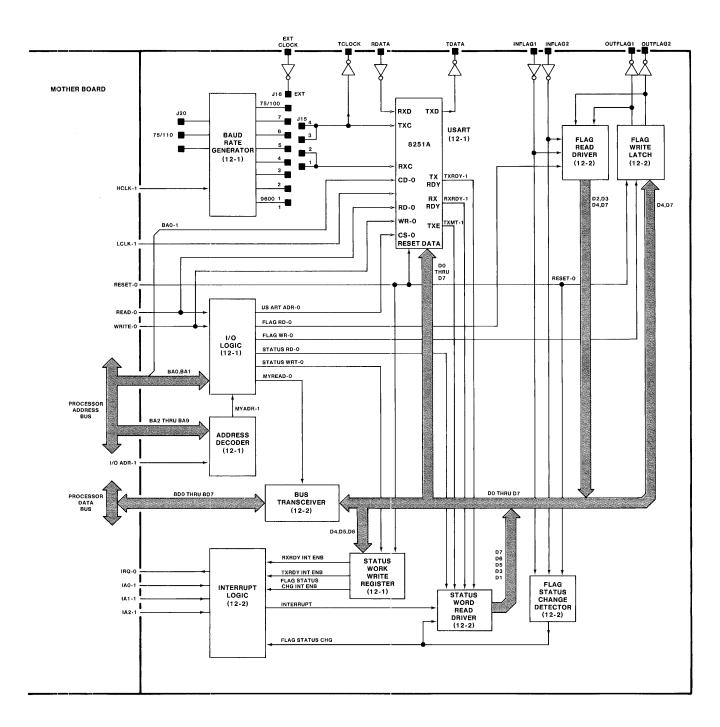

| Section 12          | OPTION 3 - RS-232 PERIPHERAL INTERFACE (4024 AND 4025)     |

|---------------------|------------------------------------------------------------|

|                     | Introduction                                               |

|                     | Summary of Characteristics12-1                             |

|                     | Circuit Descriptions12-2                                   |

|                     | USART                                                      |

|                     | Address Decoder                                            |

|                     | I/O Logic                                                  |

|                     | Status Word Write Register                                 |

|                     | Status Word Read Driver12-8                                |

|                     | Flag Write Latch12-8                                       |

|                     | Flag Read Driver                                           |

|                     | Flag Status Change Detector12-8                            |

|                     | Interrupt Logic                                            |

|                     | Baud Rate Generator12-9                                    |

|                     | Bus Transceiver                                            |

|                     | Firmware                                                   |

|                     | Initializing the RS-232 Peripheral Interface               |

|                     | Sending Characters to the Printer12-11                     |

|                     | Conding Characters to the Filmor                           |

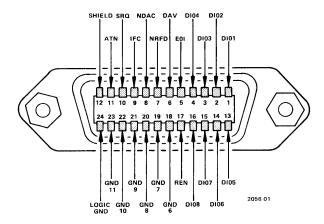

| Section 13          | OPTION 4 — GPIB PERIPHERAL INTERFACE (4025)                |

|                     | Introduction                                               |

|                     | About the GPIB13-1                                         |

|                     | Talkers, Listeners, and Controllers                        |

|                     | GPIB Interface                                             |

|                     | Handshake Sequence                                         |

|                     | GPIB Protocol: Addressing Devices for a Data Transfer 13-5 |

|                     | GPIB Code Chart13-5                                        |

|                     | I/O Registers                                              |

|                     | GPIB Firmware                                              |

|                     | Controlling and Monitoring the GPIB Lines                  |

|                     | Sending a Data Byte                                        |

|                     | Receiving a Data Byte                                      |

|                     | Circuit Descriptions                                       |

|                     | Bus Data Buffer                                            |

|                     | Address Decoder                                            |

|                     | GPIB Transceivers                                          |

|                     | GPIB Data Buffer and Latch                                 |

|                     | "Write" Half of GPIB Control Word                          |

|                     | Debouncers                                                 |

|                     | HAND Decode                                                |

|                     | Hello Gate                                                 |

|                     | "Read" Half of GPIB Control Word                           |

|                     | ATN Mask                                                   |

|                     | Handshake Steering                                         |

|                     | -                                                          |

|                     | Handshake Logic                                            |

| 1005 05DVIOE VOL. 4 | Interrupt Control Circuitry13-18                           |

| Section 14 | OPTIONS 10 AND 11 — POLLING                         |

|------------|-----------------------------------------------------|

|            | Introduction                                        |

|            | Tektronix Polling System                            |

|            | The Current Loop and Option 10                      |

| Section 15 | OPTIONS 23 TO 26 — GRAPHICS MEMORY (4025 ONLY)      |

|            | Introduction                                        |

|            | Parts Included15-1                                  |

|            | 4025 Graphics Concepts: What the Firmware Does 15-1 |

|            | GRAPHIC Command15-2                                 |

|            | VECTOR Command15-3                                  |

|            | I/O Registers15-4                                   |

|            | Firmware Details                                    |

|            | Graphics Memory Board Circuitry                     |

|            | Block Diagram15-9                                   |

|            | Dot Pattern Memory                                  |

|            | Scrunch Memory15-14                                 |

|            | RAM Control Circuitry                               |

|            | RAM Address Circuitry                               |

|            | RAM Cycle Requestor                                 |

|            | Timing Circuitry15-26                               |

|            | Processor Interface Circuitry15-28                  |

| Section 16 | OPTION 31 — CHARACTER SET EXPANSION (4025 ONLY)     |

|            | Introduction                                        |

|            | Inputs and Outputs16-1                              |

|            | Modes of Operation                                  |

|            | Circuit Descriptions16-4                            |

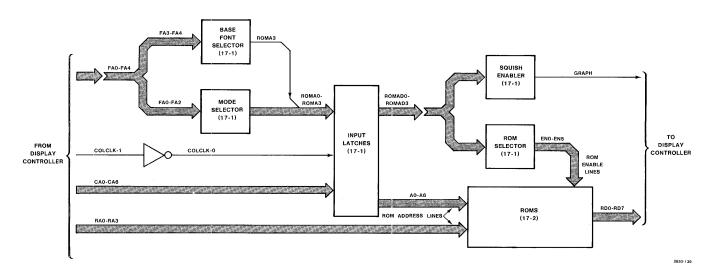

|            | Block Diagram16-4                                   |

|            | Base Font Selector16-4                              |

|            | Mode Selector                                       |

|            | Input Latches                                       |

|            | ROM Selector16-6                                    |

|            | Squish Enabler16-7                                  |

|            | ROMs 16-7                                           |

| Section 17 | OPTIONS 32 AND 34 — RULINGS AND MATH CHARACTERS     |

|            | Option 32: Rulings Characters (4024 and 4025)17-1   |

|            | Option 34: Math Characters (4025 only)17-4          |

| Section 18   | OPTION 35 — ROM EXPANSION (4025 ONLY)  |

|--------------|----------------------------------------|

|              | Introduction18-1                       |

|              | Purpose of Option 3518-1               |

|              | Two Different Circuit Boards18-1       |

|              | ROM Expansion Board (670-5729-XX)      |

|              | Inputs and Outputs18-2                 |

|              | Circuit Descriptions                   |

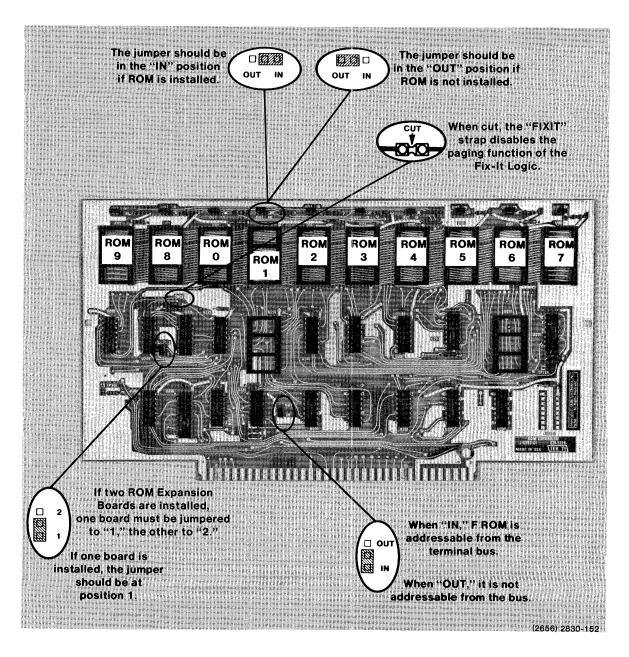

|              | Strappable Options and Test Points18-7 |

|              | ROM Option Board (670-5064-XX)         |

|              | Fix-It                                 |

| Section 19   | OTHER OPTIONS                          |

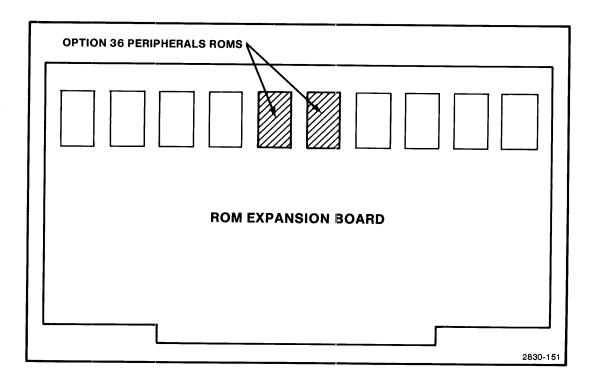

|              | Option 36 — Peripherals ROM19-1        |

|              | Option 40 — Hard Copy and Video Out    |

|              | Option 41 — Self Test 19-2             |

|              | Option 48 — 220V, 50Hz19-2             |

| Appendix A   | EXAMPLES OF COMMANDS                   |

| Appendix B   | ASCII CODE CHART                       |

| Appendix C   | SPECIFICATIONS                         |

| rippolidix O | or con tox troito                      |

|              | INDEX                                  |

# **ILLUSTRATIONS**

| Figure | Description                                              | Page   |

|--------|----------------------------------------------------------|--------|

| 1-1    | 4024 and 4025 Computer Display Terminals                 |        |

| 2-1    | 4024 System Block Diagram                                | . 2-2  |

| 2-2    | 4025 System Block Diagram                                | . 2-3  |

| 2-3    | 4024 Memory Map                                          | . 2-4  |

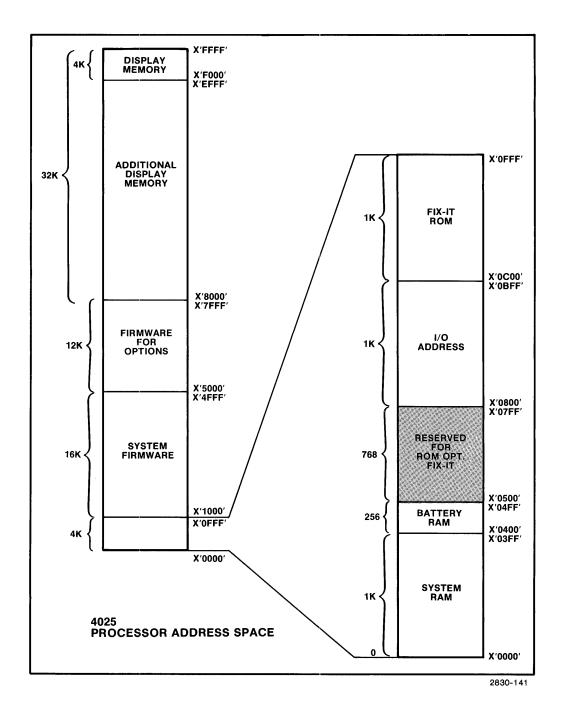

| 2-4    | 4025 Memory Map                                          | . 2-5  |

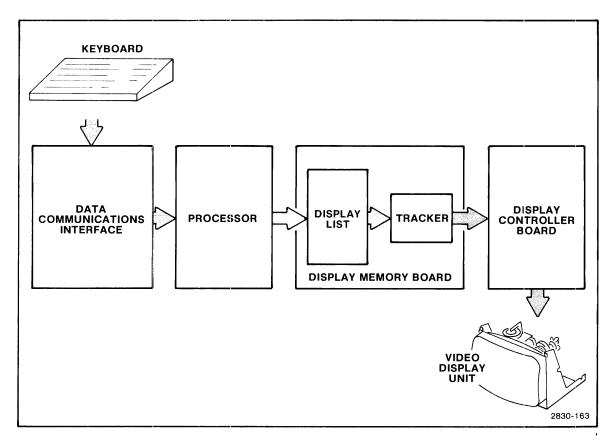

| 2-5    | Flow of Information from Keyboard to Screen              | . 2-10 |

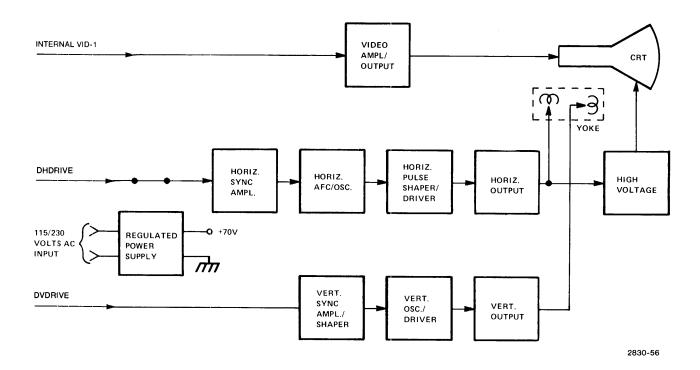

| 3-1    | Video Display Unit Block Diagram                         |        |

| 3-2    | Display Power Supply                                     |        |

| 3-3    | Video Amplifier                                          |        |

| 3-4    | Horizontal Sync Amplifier                                | . 3-4  |

| 3-5    | Phase Detector and Horizontal Oscillator                 |        |

| 3-6    | Horizontal Pulse Shaper and Driver                       |        |

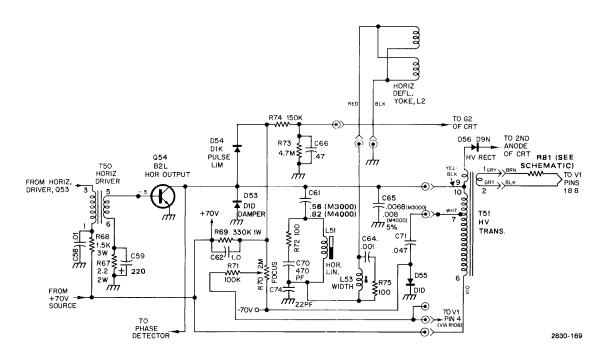

| 3-7    | Horizontal Output Circuit                                |        |

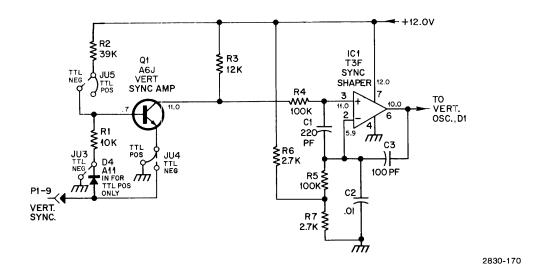

| 3-8    | Vertical Sync Amplifier and Sync Shaper                  |        |

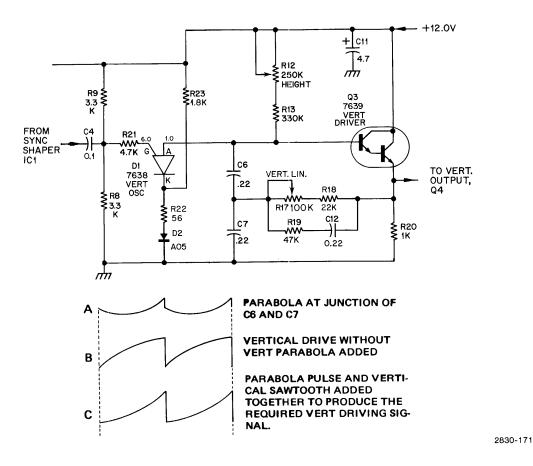

| 3-9    | Vertical Oscillator/Driver                               |        |

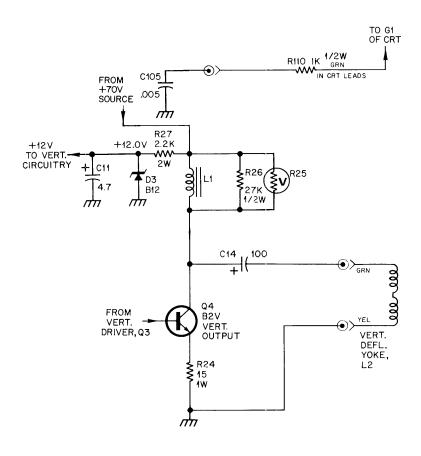

| 3-10   | Vertical Output Circuit                                  | . 3-11 |

| 3-11   | Bus Connector Pin Identification                         | . 3-14 |

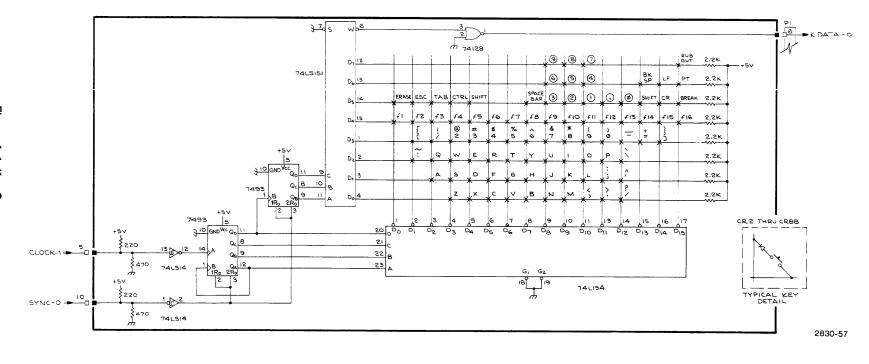

| 4-1    | Key Scanner                                              | . 4-2  |

| 4-2    | Lights and Bell Circuitry                                | . 4-3  |

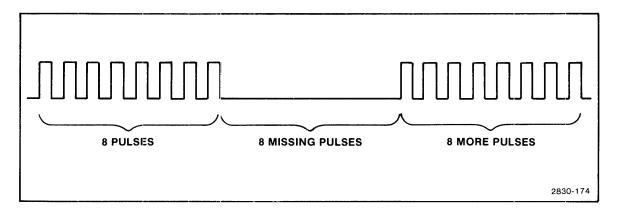

| 4-3    | SCLK Waveform                                            |        |

| 5-1    | 4025 Processor Board Block Diagram                       | . 5-3  |

| 5-2    | Location of System Firmware in 4025 Memory Address Space | . 5-6  |

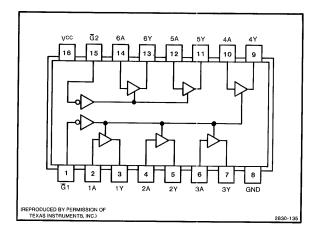

| 5-3    | 74LS367 Tri-State Buffers                                | . 5-7  |

| 5-4    | Interrupt Control Circuitry                              | . 5-13 |

| 5-5    | 4025 Processor Board Memory Map                          | . 5-21 |

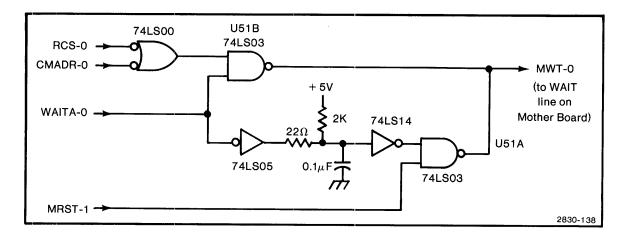

| 5-6    | Logic for Generating the MWT Signal                      | . 5-23 |

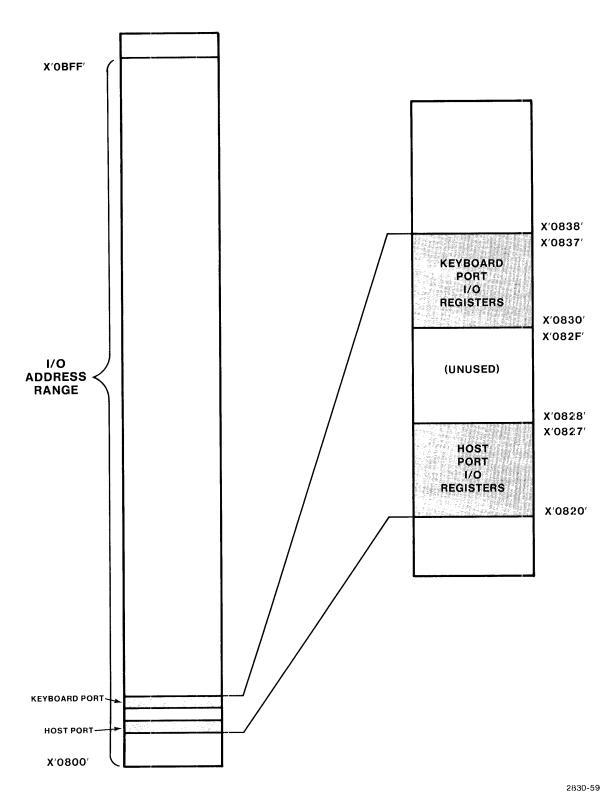

| 6-1    | Location of Host and Keyboard Ports in I/O Address Space | . 6-2  |

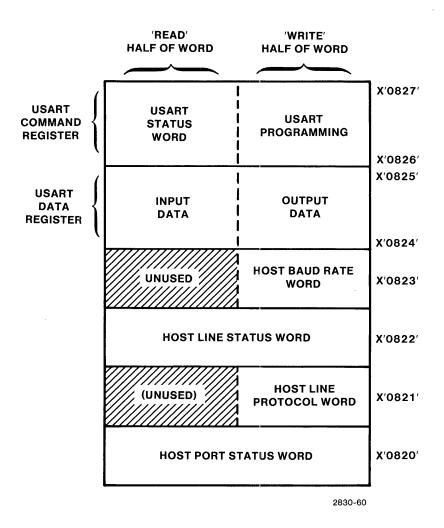

| 6-2    | Host Port Memory Map                                     | . 6-3  |

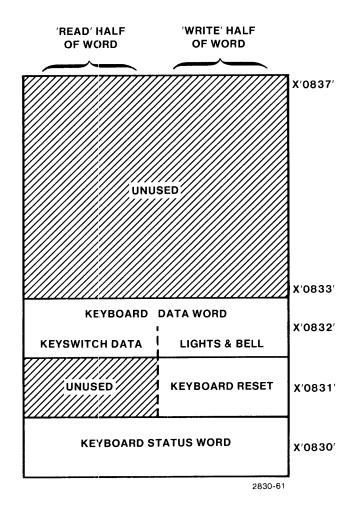

| 6-3    | Keyboard Port Memory Map                                 | . 6-4  |

| 6-4    | Communications Interface Board Block Diagram             | . 6-7  |

| 6-5    | Asynchronous and Synchronous Serial Data Formats         | . 6-11 |

| 6-6    | Host Port Block Diagram                                  | . 6-18 |

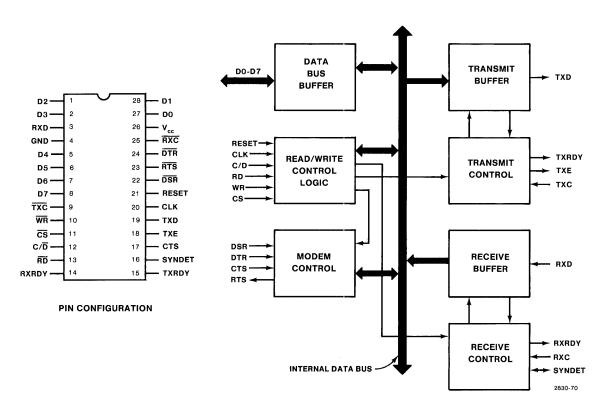

| 6-7    | 8251A USART                                              | . 6-19 |

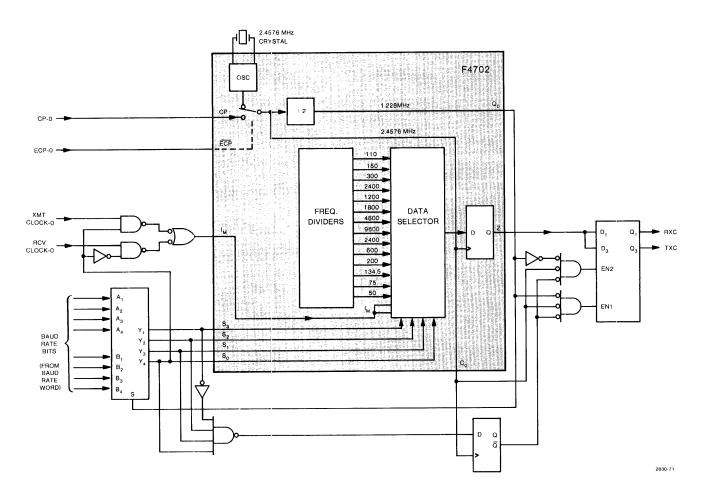

| 6-8    | Baud Rate Generator                                      | . 6-22 |

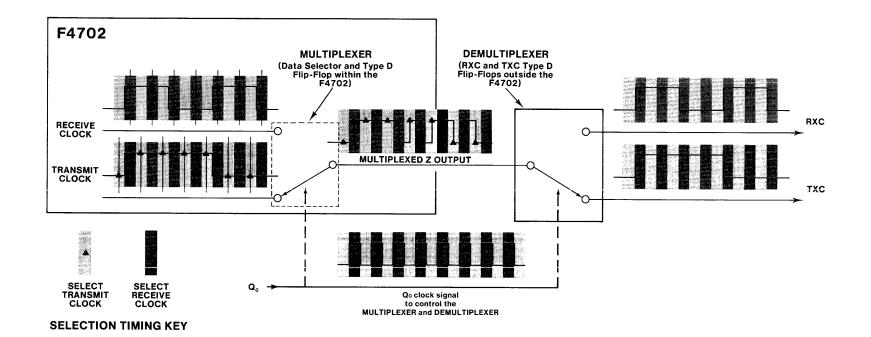

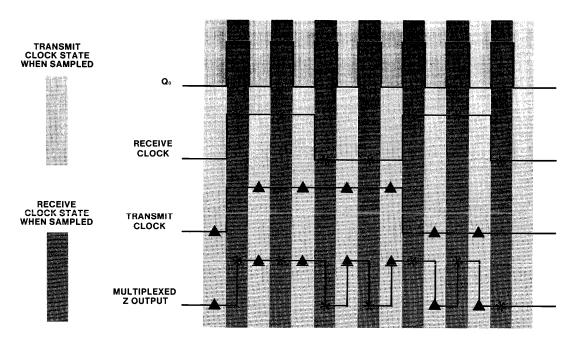

| 6-9    | Multiplexing and Demultiplexing the Baud Rate Clocks     | . 6-24 |

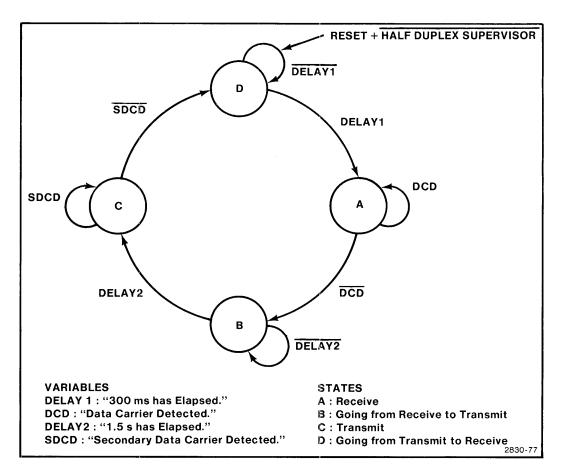

| 6-10   | Line Turnaround State Diagram                            | . 6-31 |

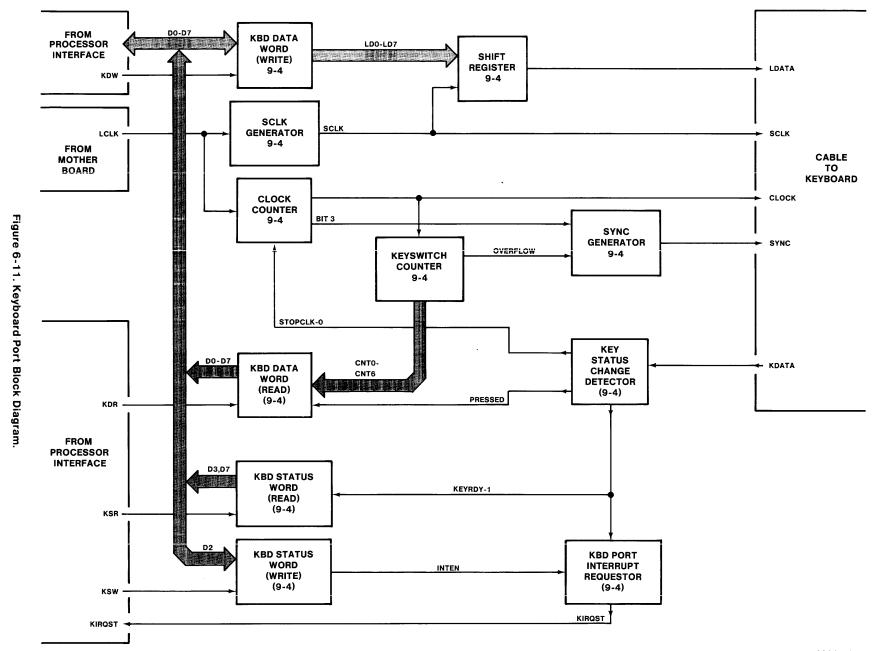

| 6-11   | Keyboard Port Block Diagram                              |        |

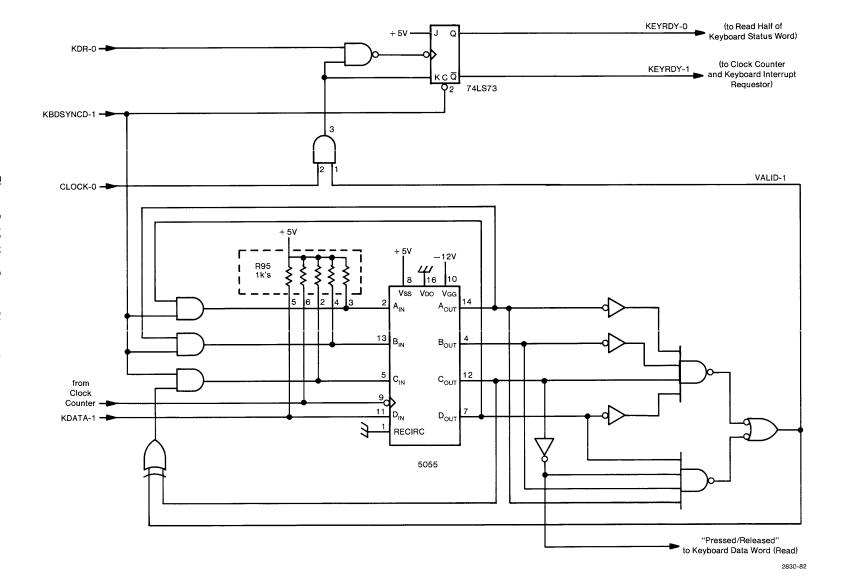

| 6-12   | Key Status Change Detector                               | . 6-39 |

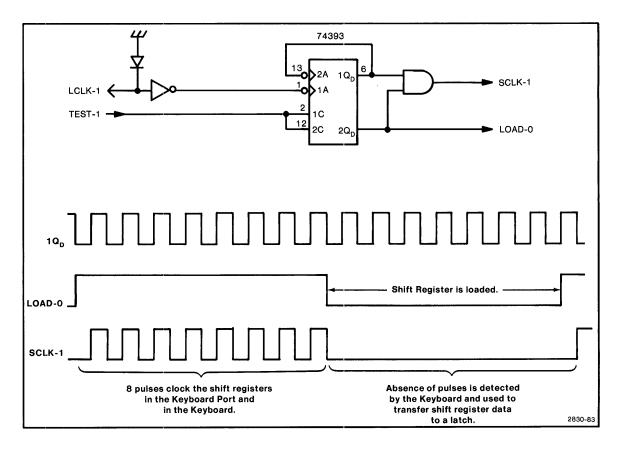

| 6-13   | SCLK Generator and Waveforms                             | . 6-41 |

| Figure | Description                                        | Page    |

|--------|----------------------------------------------------|---------|

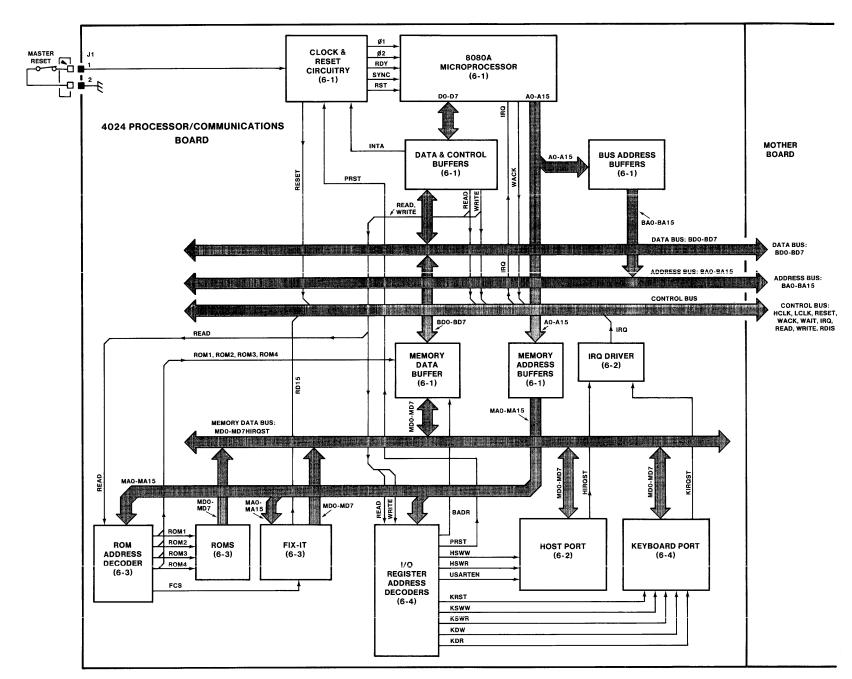

| 7-1    | 4024 Processor/Comm. Board Block Diagram           | . 7-2   |

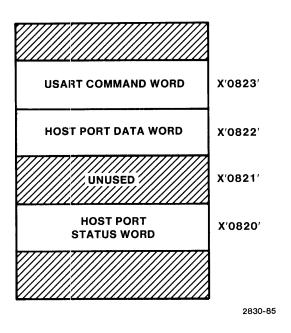

| 7-2    | 4024 Host Port Memory Map                          | . 7-6   |

| 8-1    | Display Memory Board Block Diagram                 | . 8-4   |

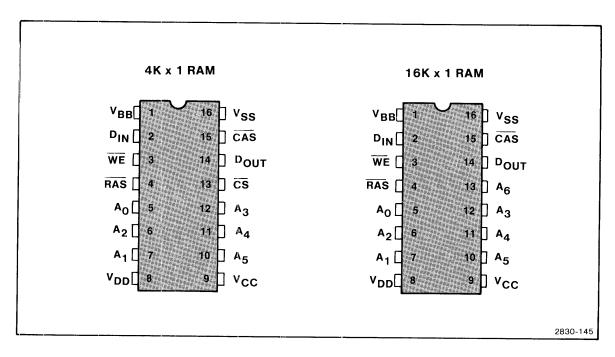

| 8-2    | Pinouts for 4K and 16K RAMs                        | . 8-5   |

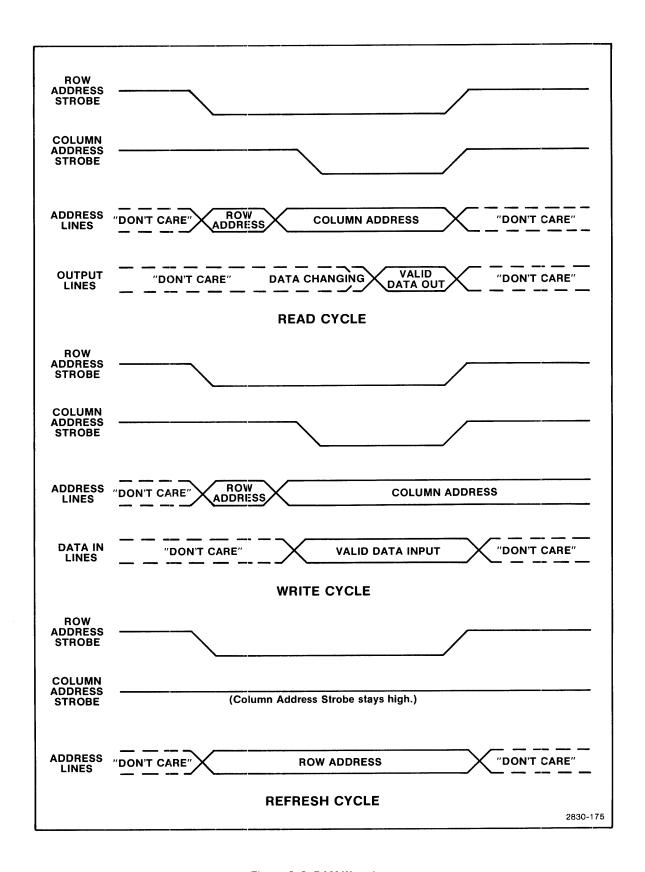

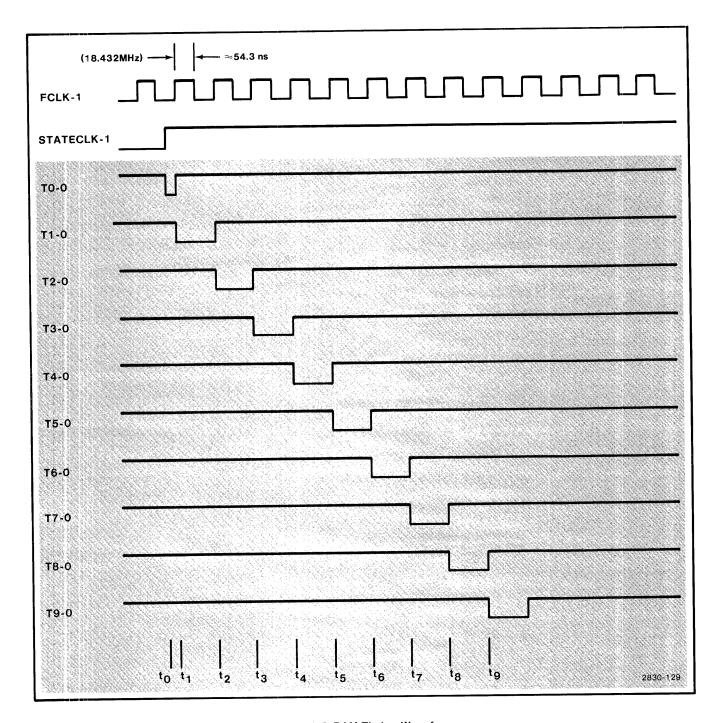

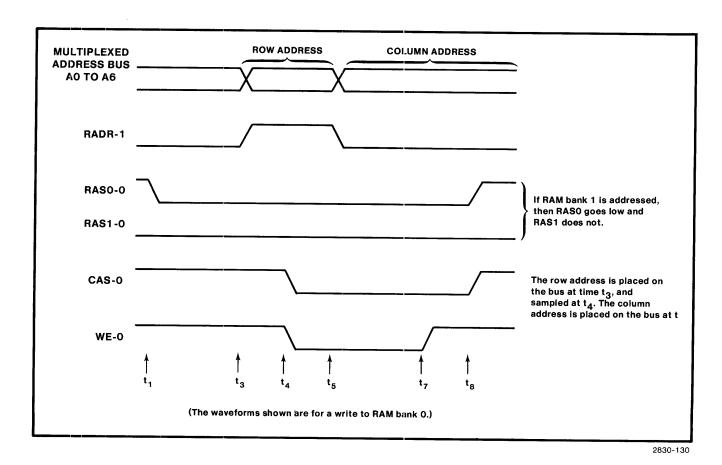

| 8-3    | RAM Waveforms                                      | . 8-6   |

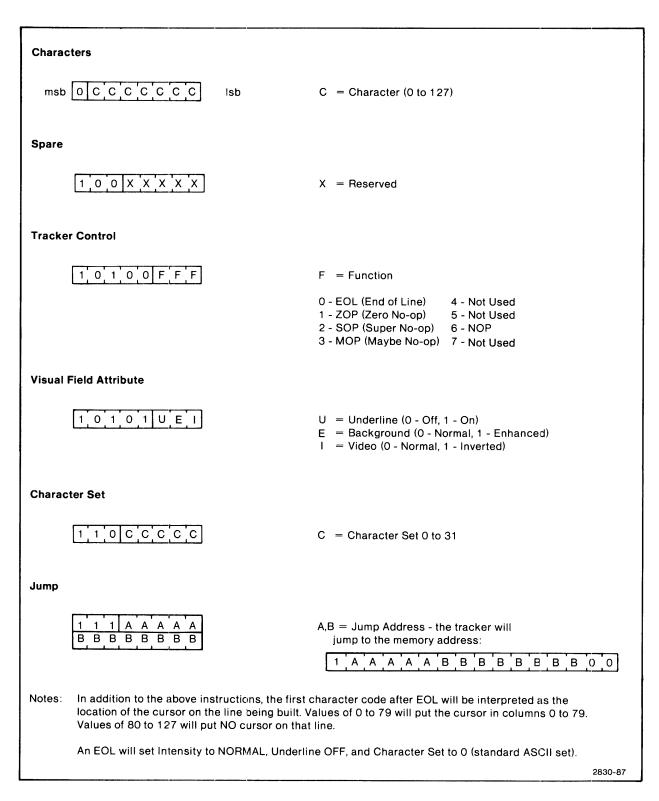

| 8-4    | Display List Instruction Formats                   | . 8-12  |

| 9-1    | Raster Scan Display                                | . 9-4   |

| 9-2    | Simplified Display Controller Block Diagram        | . 9-6   |

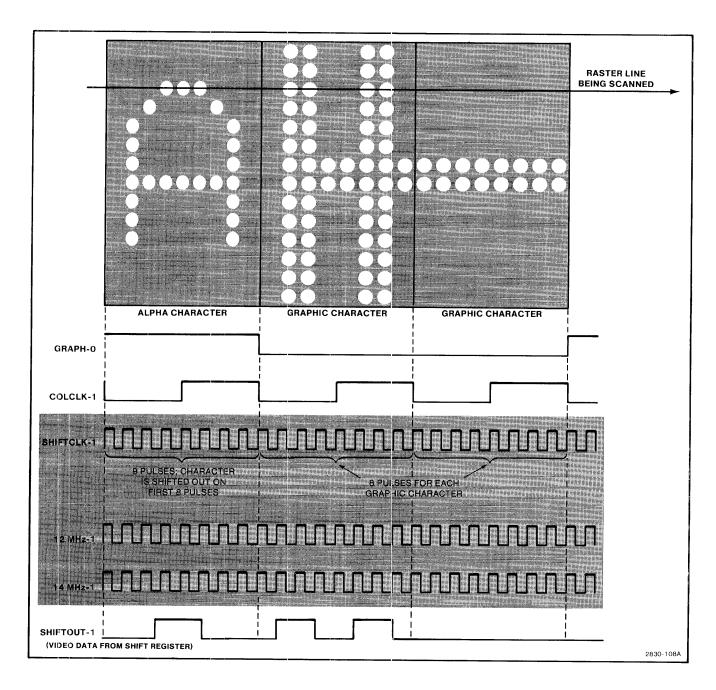

| 9-3    | Video Pipeline                                     | . 9-9   |

| 9-4    | 4025 Display Controller Block Diagram              | . 9-12  |

| 9-5    | 4025 Display List Decoder                          | . 9-14  |

| 9-6    | 4025 Row Buffers                                   | . 9-17  |

| 9-7    | Buffer Control Waveforms                           | . 9-19  |

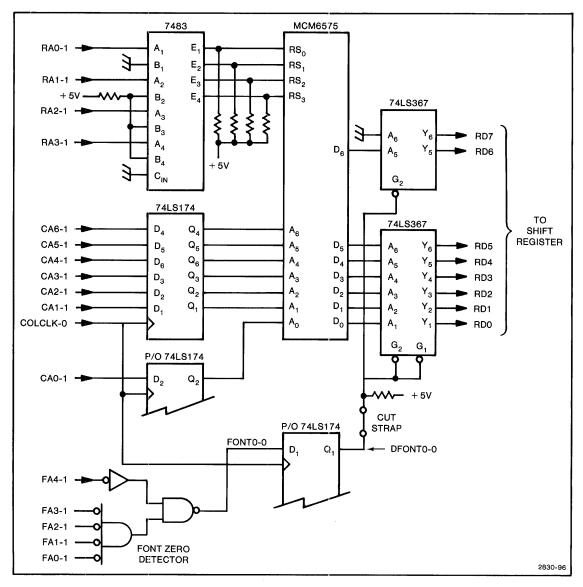

| 9-8    | 4025 Character Set Memory                          | . 9-20  |

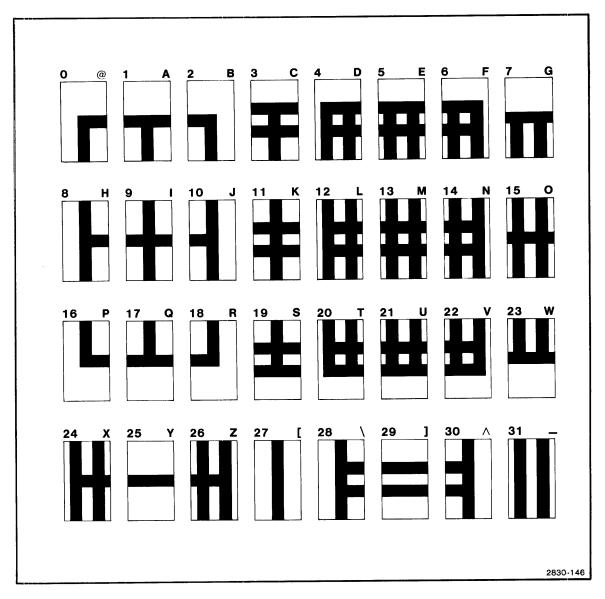

| 9-9    | Standard Character Font                            | . 9-21  |

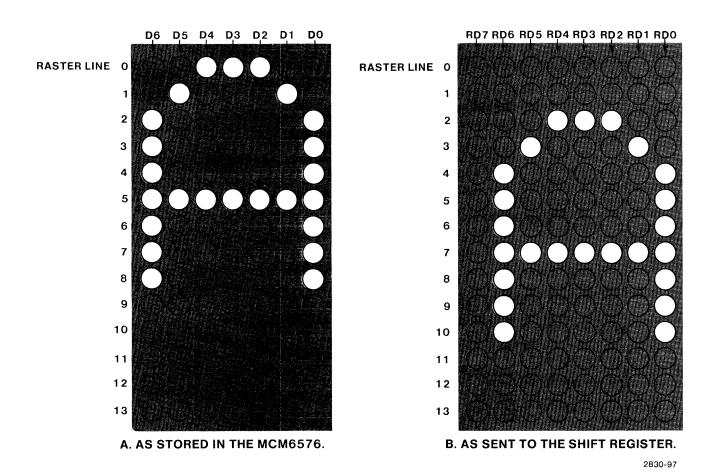

| 9-10   | A Character's Dot Matrix Pattern                   | . 9-22  |

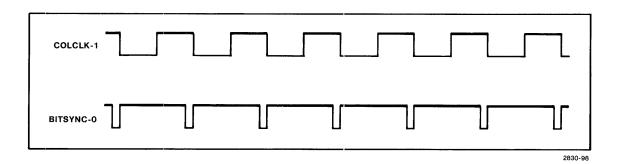

| 9-11   | COLCLK and BITSYNC                                 | . 9-25  |

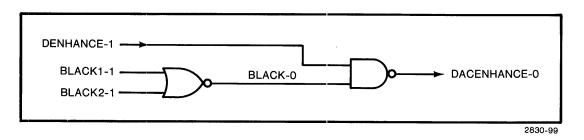

| 9-12   | Generating the DACENHANCE Signal                   | . 9-27  |

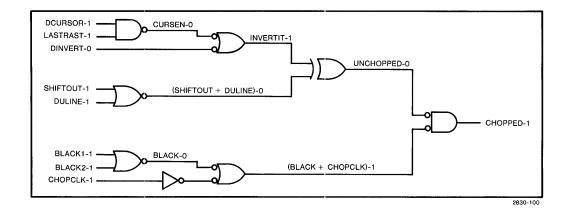

| 9-13   | Generating the Chopped Video Signal                | . 9-27  |

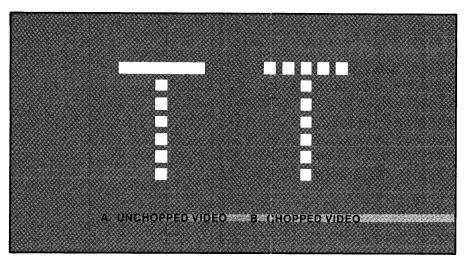

| 9-14   | Effect of Chopping the Video Signal                | . 9-29  |

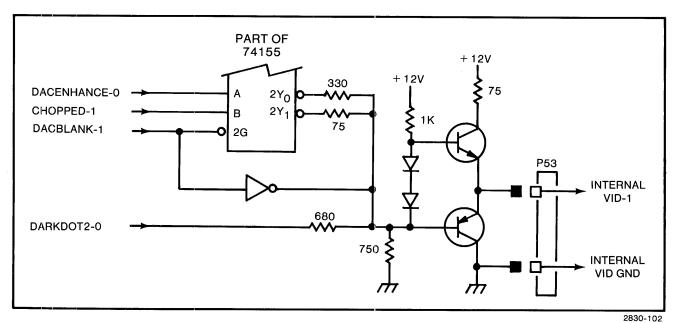

| 9-15   | Internal Video Digital-to-Analog Converter         | . 9-31  |

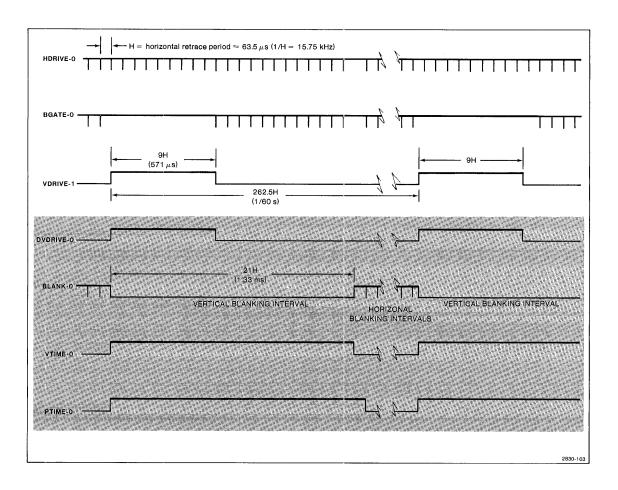

| 9-16   | Vertical Retrace Signals                           | . 9-33  |

| 9-17   | Text Row Signals                                   | . 9-34  |

| 9-18   | Horizontal Retrace Signals                         | . 9-35  |

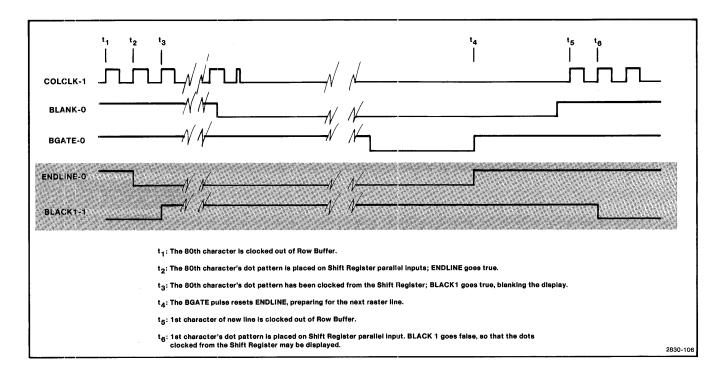

| 9-19   | ENDLINE and BLACK1 Signals                         | . 9-37  |

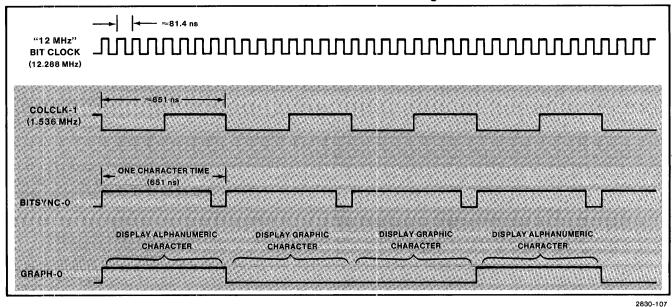

| 9-20   | Character Time Signals                             | . 9-37  |

| 9-21   | Dot Time Signals                                   | . 9-39  |

| 9-22   | Video Timing Circuitry                             | . 9-41  |

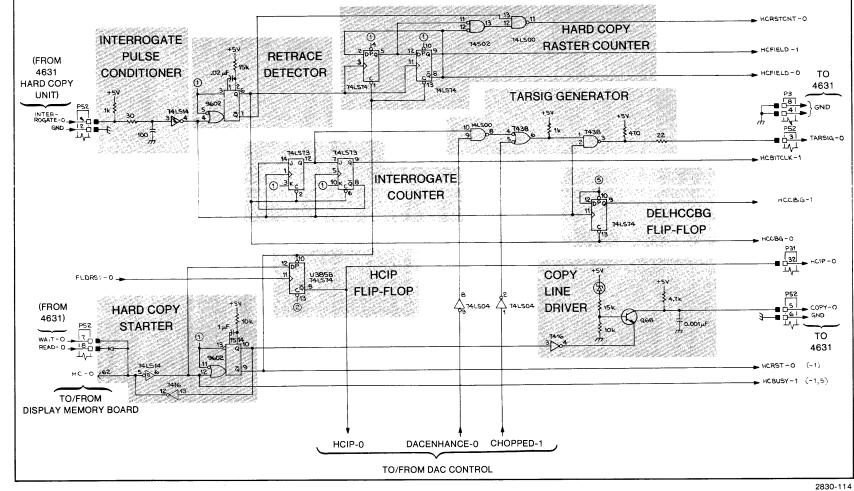

| 9-23   | Hard Copy Interconnections                         | . 9-47  |

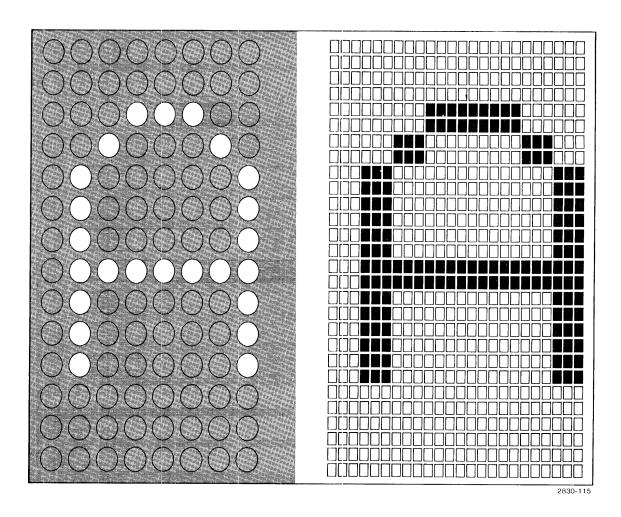

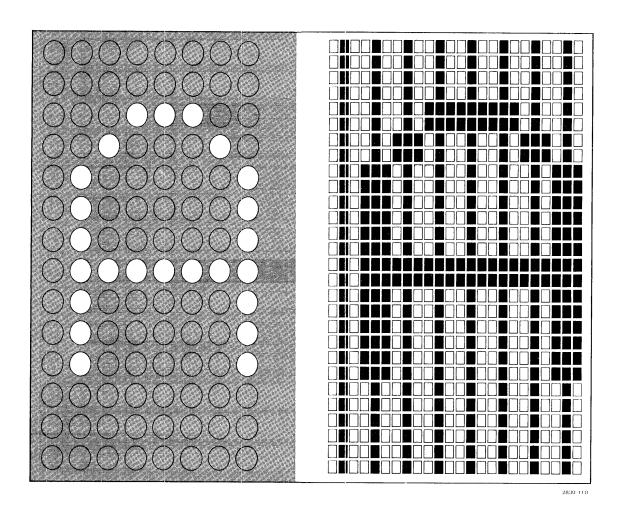

| 9-24   | Video and Hard Copy Representations of a Character | . 9-49  |

| 9-25   | Hard Copy Circuitry                                | . 9-50  |

| 9-26   | Video and Hard Copy Representations of a Character |         |

|        | Displayed with Enhanced Background                 | . 9-53  |

| 9-27   | 4024 Display Controller Block Diagram              | . 9-55  |

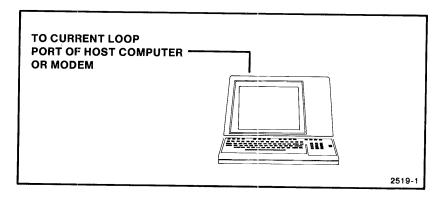

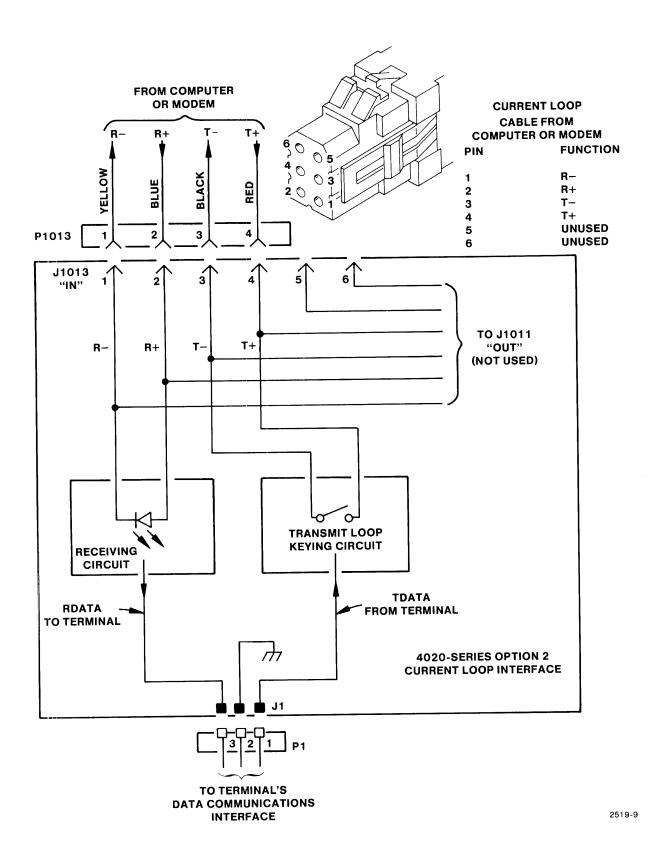

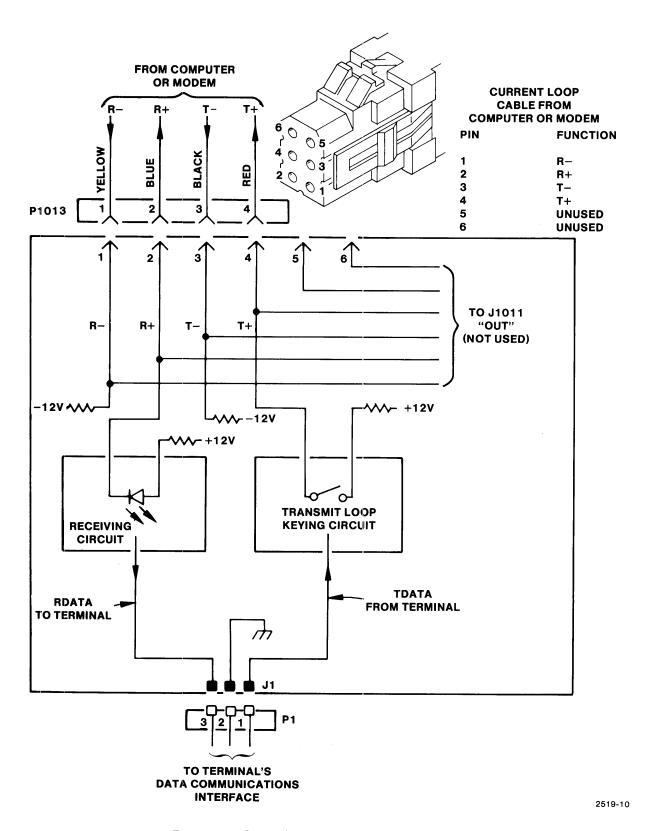

| 11-1   | Current Loop Connecting Terminal to Host Computer  | . 11-1  |

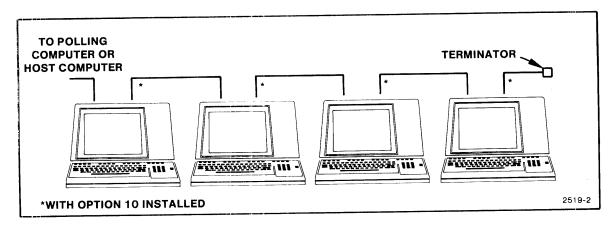

| 11-2   | Multiple Terminals on the Same Current Loop        | . 11-2  |

| 11-3   | Option 2 Block Diagram in PASSIVE Mode             | . 11-4  |

| 11-4   | Option 2 Block Diagram in ACTIVE Mode              | . 11-5  |

| 12-1   | RS-232 Peripheral Interface Board Block Diagram    |         |

| 13-1   | GPIB Connector                                     | . 13-2  |

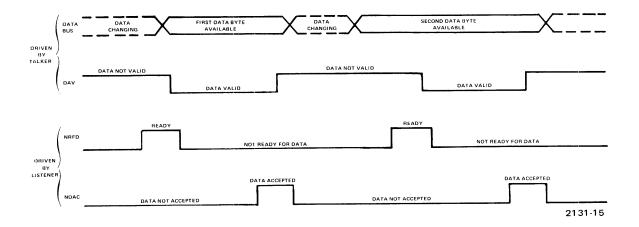

| 13-2   | GPIB Transfer Bus Handshake Sequence               | . 13-4  |

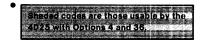

| 13-3   | GPIB Peripheral Interface Board Block Diagram      |         |

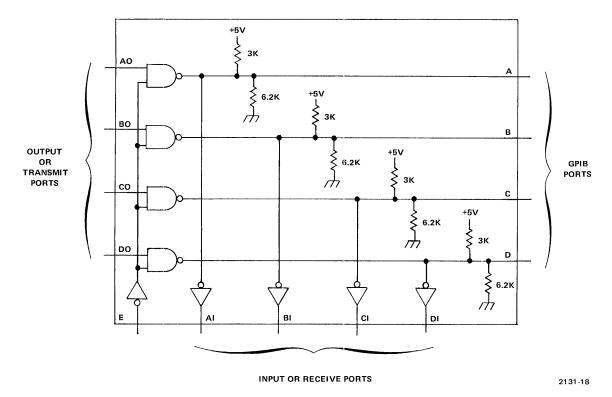

| 13-4   | GPIB Transceiver                                   | . 13-13 |

| Figure | Description                                    | Page  |

|--------|------------------------------------------------|-------|

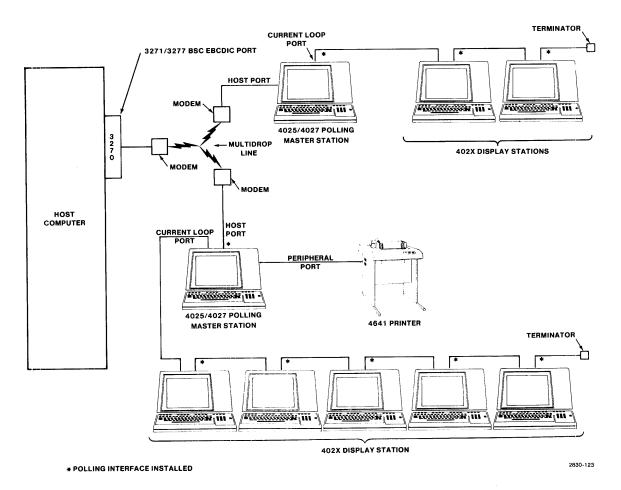

| 14-1   | 4020-Series Polling System                     | 14-2  |

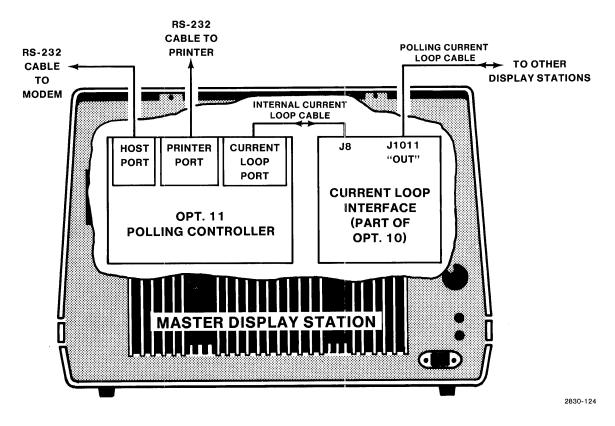

| 14-2   | Master Display Station Interconnections        | 14-3  |

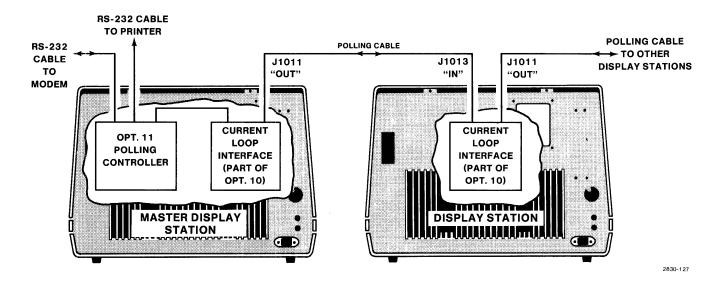

| 14-3   | Display Station Interconnections               | 14-4  |

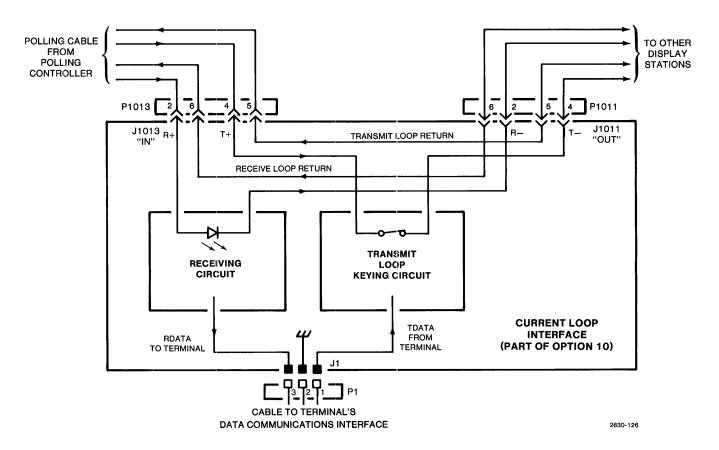

| 14-4   | Current Loop Interface, as Used with Option 10 | 14-5  |

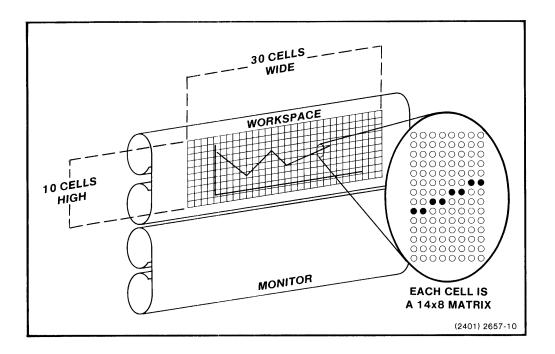

| 15-1   | A Graphic Area                                 | 15-2  |

| 15-2   | Graphics Memory Board Block Diagram            | 15-10 |

| 15-3   | Pinouts for 4K and 16K RAMs                    | 15-11 |

| 15-4   | RAM Waveforms                                  | 15-12 |

| 15-5   | RAM Timing Waveforms                           | 15-16 |

| 15-6   | RAM Control Waveforms During a Write           |       |

|        | to Bank 0 of Graphics RAM                      | 15-17 |

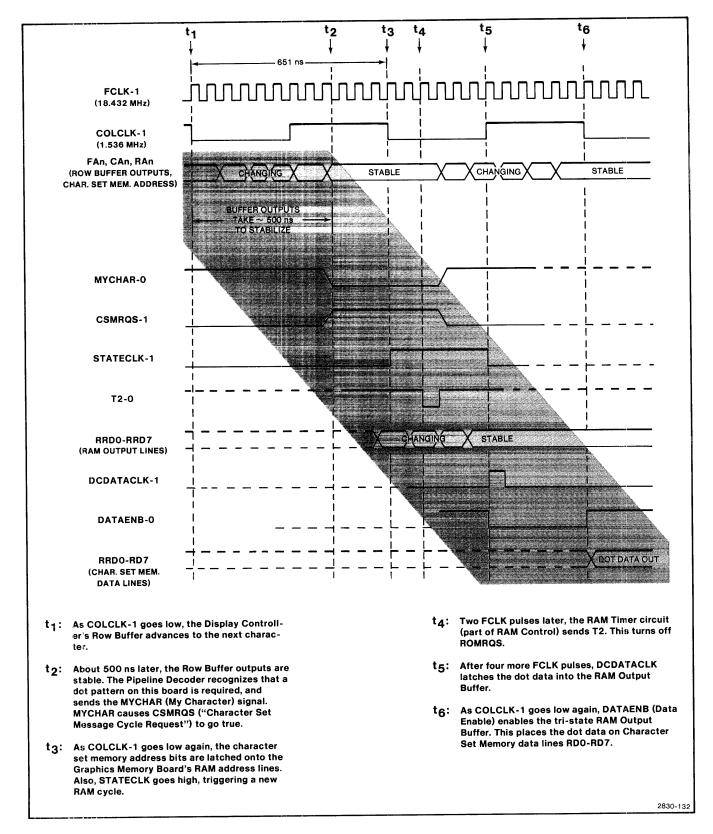

| 15-7   | Graphics Memory Timing During a CSM Cycle      | 15-24 |

| 16-1   | Character Set Expansion Board Block Diagram    | 16-5  |

| 17-1   | 4024/4025 Rulings Characters                   | 17-2  |

| 17-2   | 4025 (Only) Rulings Characters                 | 17-3  |

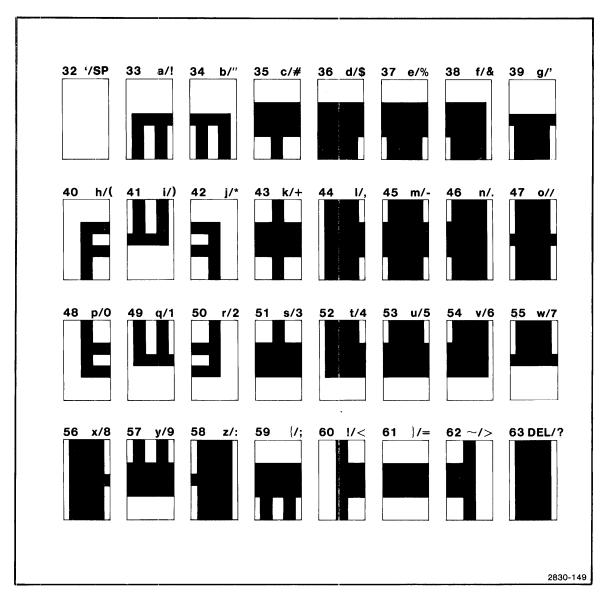

| 17-3   | Math Characters                                | 17-5  |

| 18-1   | ROM Expansion Board Block Diagram              | 18-3  |

| 18-2   | ROM Expansion Board Strap Settings             | 18-7  |

| 19-1   | Location of Option 36 Peripherals ROMs         | 19-1  |

# **TABLES**

| Table | Description                                              | Page  |

|-------|----------------------------------------------------------|-------|

| 1-1   | 4024/4025 Options Summary                                | 1-3   |

| 3-1   | Mother Board Signal Lines                                | 3-15  |

| 6-1   | 4025 Host Port I/O Registers                             | 6-5   |

| 6-2   | 4025 Keyboard Port I/O Registers                         | 6-6   |

| 6-3   | Baud Rate Generator Programming                          | 6-25  |

| 6-4   | Line Protocol Bits                                       | 6-27  |

| 7-1   | 4024 Host Port I/O Registers                             | 7-7   |

| 7-2   | 4024 Keyboard Port I/O Registers                         | 7-8   |

| 8-1   | Display Memory Board I/O Registers                       | 8-19  |

| 9-1   | Signals at Display Controller Connector J31              | 9-24  |

| 10-1  | Option 1 Half Duplex Commands                            | 10-1  |

| 12-1  | USART I/O Truth Table                                    | 12-4  |

| 12-2  | RS-232 Peripheral Interface I/O Registers                | 12-6  |

| 12-3  | RS-232 Peripheral Interface I/O Logic Truth Table        | 12-7  |

| 13-1  | GPIB Code Chart                                          | 13-6  |

| 13-2  | GPIB Board I/O Registers                                 | 13-7  |

| 15-1  | Graphics Memory Board I/O Registers                      | 15-5  |

| 15-2  | PIPELINE DECODE and ADDRESS MAPPING Strap Settings       | 15-20 |

| 16-1  | Character Fonts on the Character Set Expansion Board     | 16-3  |

| 16-2  | Selecting Base Font on the Character Set Expansion Board | 16-5  |

| B-1   | ASCII Code Chart                                         | B-1   |

| B-2   | Control Characters                                       | B-2   |

| C-1   | Display Mechanism                                        | C-1   |

| C-2   | Display Characteristics                                  | C-2   |

| C-3   | Interface Characteristics                                | C-3   |

| C-4   | Buffering and Editing Capabilities                       | C-4   |

| C-5   | Keyboard Specifications                                  | C-4   |

| C-6   | Graphics Specifications                                  | C-5   |

| C-7   | Physical Characteristics                                 | C-6   |

| C-8   | Power Requirements                                       | C-6   |

Figure 1-1. 4024 and 4025 Computer Display Terminals.

# Section 1

# INTRODUCTION

#### **ABOUT THIS MANUAL**

The service documentation for the 4024 and 4025 Computer Display Terminals consists of two volumes. Volume 1 (this volume) contains the circuit descriptions. Volume 2 contains installation procedures, calibration procedures, block diagrams, schematics, and parts lists.

Additional information is available in the following manuals:

- 4024 Computer Display Terminal Operator's Manual.

- 4025 Computer Display Terminal Operator's Manual.

- 4024/4025 Computer Display Terminal Programmer's Reference Manual.

- 4024/4025 Programmer's Reference Guide.

- 4025 Option 41 / 851 Diagnostic Instruction Manual.

- 4020 Series Polling Reference Manual.

- 4020 Series Polling Service Manual.

#### **ABOUT THE TERMINALS**

#### **Basic Characteristics**

The 4024 and 4025 Computer Display Terminals use a raster scan video display (an internal video monitor). The display uses a 525-line, 60-Hz interlaced raster scan, like that in American television sets. A long-persistence green phosphor minimizes flicker and reduces eyestrain.

Both terminals include an 8080 microprocessor, whose programs are stored in ROM (read only memory). The microprocessor oversees all aspects of the terminal's operation: storing text and graphic information in internal memory, communicating with the host computer and with peripheral devices, interpreting and executing commands from the operator and the computer, etc.

Although the terminal includes a microprocessor, it is not programmable by the user. The terminal will accept a list of commands, and execute them in the order of receipt. However, there are no 4024/4025 commands for "add two numbers" or "go back to step 6 of the program." The only commands are for such functions as "change the baud rate," "send the stored text to the computer," or "draw a vector on the screen."

#### Differences Between 4024 and 4025

The 4024 is a simplified version of the 4025. The differences are:

- The 4025 has more card slots in its Mother Board than the 4024, and it has many more options available. Options available for the 4025, but not for the 4024, include:

- Graphics

- Character Set Expansion

- GPIB Interface

- Half Duplex Data Communications

- Polling Controller

- The 4025's Display Controller can drive a hard copy unit or an external video monitor. Besides its standard character font, it can consult ROMs on a Character Set Expansion Board to display 64 different rulings characters, special math characters, or characters of different alphabets. It may also consult RAMs on a Graphics Memory Board to display graphic information or user-defined character fonts. The 4025 Display Controller can generate enhanced backgrounds, inverted video, and underlines to give special emphasis to portions of the displayed text.

The 4024's Display Controller, on the other hand, is much more limited. It cannot drive a hard copy unit or external video monitor. It cannot display inverted video or underlines, although it can generate the "enhanced" background. The only character fonts it can display are the standard font and 32 rulings characters.

#### **Options**

Table 1-1 lists the options available for the 4024 and 4025.

#### Table 1-1

## 4024/4025 OPTIONS SUMMARY

| 4024 Option    | 4025 Option       | Name                           | Description                                                                                                                                                                                                          |

|----------------|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _              | 1                 | HALF DUPLEX                    | Permits Half Duplex Normal and Half Duplex with<br>Supervisor data communications. Requires Op-<br>tion 35.                                                                                                          |

| 2              | 2                 | CURRENT LOOP                   | Permits the terminal to communicate with the host computer by means of a 20 mA current loop, instead of the standard RS-232 interface.                                                                               |

| 3              | 3                 | RS-232 PERIPHERAL<br>INTERFACE | Provides communications with RS-232 peripheral devices, such as the TEKTRONIX 4642 Printer. In the 4025, requires Options 35 and 36.                                                                                 |

| _              | 4                 | GPIB PERIPHERAL IN-<br>TERFACE | Provides communications with GPIB peripherals—4924 Tape Drive and 4662 Plotter. Requires Options 35 and 36.                                                                                                          |

| 10             | 10                | POLLING INTERFACE              | Permits the terminal to be one of up to eight display stations communicating over a 20 mA current loop with the same Option 11 Polling Controller, and communicating through that Controller with the host computer. |

| <del>-</del> , | 11                | POLLING CONTROLLER             | Provides full duplex interface up to 4800 baud.<br>Also controls up to eight 4024/4025 terminals,<br>including the terminal in which the Polling<br>Controller is installed.                                         |

| 20, 21,<br>22  | 20, 21,<br>22     | ADDITIONAL DISPLAY<br>MEMORY   | Provides additional display memory for a total of 8K, 16K, or 32K eight-bit words.                                                                                                                                   |

| _              | 23, 24,<br>25, 26 | GRAPHICS MEMORY                | Provides 4K, 8K, 16K, or 32K of graphics memory.<br>Also provides the firmware for drawing graphs in<br>the workspace. Requires Option 35.                                                                           |

| _              | 31                | CHARACTER EXPAN-<br>SION       | Provides the Character Set Expansion Board, on which ROMs holding optional character sets can be placed.                                                                                                             |

| 32             | 32                | RULINGS CHARACTERS             | A ROM holding the rulings characters set. In the 4025, requires Option 31.                                                                                                                                           |

|                | 34                | MATH CHARACTERS                | A ROM holding the math character set. Requires Option 31.                                                                                                                                                            |

| _              | 35                | ROM EXPANSION                  | Provides the ROM Expansion Board, in which ROMs holding optional firmware can be inserted.                                                                                                                           |

| _              | 36                | PERIPHERALS ROM                | Provides firmware to drive RS-232 compatible printers (when used with Option 3), or the 4924 Tape Drive and the 4662 Plotter (when used with Option 4). Requires Option 35.                                          |

| _              | 40                | HARD COPY AND VIDEO<br>OUT     | Provides hard copy capability with TEKTRONIX 4631 Hard Copy Unit. Also provides a BNC connector for attaching an external video monitor.                                                                             |

|                | 41                | SELF TEST                      | Extended test to provide fault isolation. Requires Option 35.                                                                                                                                                        |

| 48             | 48                | 220 VOLTS, 50 HZ               |                                                                                                                                                                                                                      |

|                |                   |                                |                                                                                                                                                                                                                      |

#### INTRODUCTION

#### **Accessories**

The standard and optional accessories for the 4024 and 4025 are:

#### Standard Accessories

4024 Computer Display Terminal Operator's Manual 4025 Computer Display Terminal Operator's Manual Keyboard Overlay (blank)

Blank Key Cap (1 x 2)

Blank Key Cap (1 x 1)

Key Cap Cover (1 x 2)

Key Cap Cover (1 x 1)

Power Cord

#### • Optional Accessories

4024/4025 Service Manual (Two Volumes) 4024/4025 Programmer's Reference Manual 4024/4025 Programmer's Reference Card

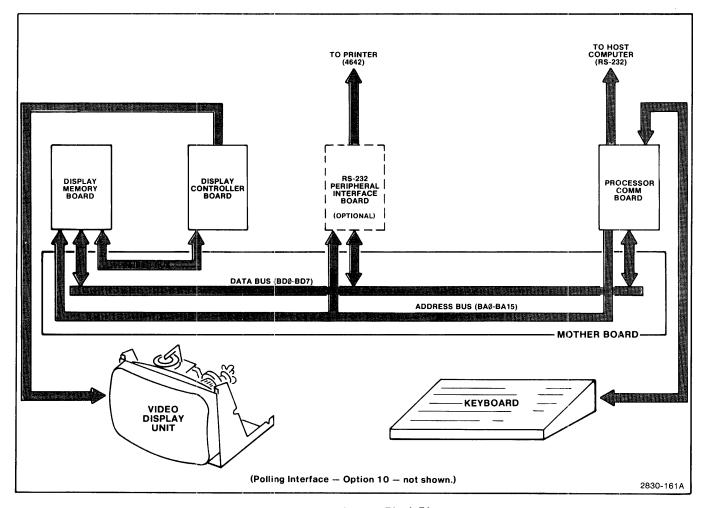

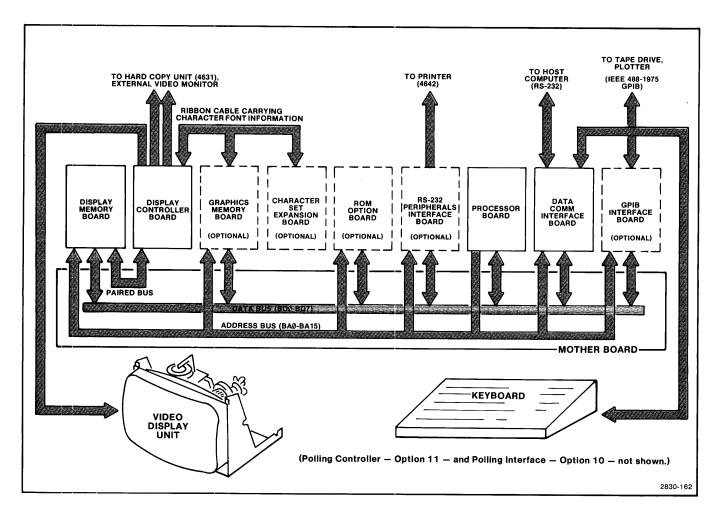

# Section 2

# SYSTEM OVERVIEW

Refer to Figures 2-1 and 2-2, the system block diagrams for the 4024 and the 4025. The basic differences between the terminals are:

- The 4025 has room for nine boards in its Mother Board, while the 4024 has room for only four boards.

- The 4025 has separate Processor and Data Communications boards; in the 4024, these are combined on a single board, the Processor/Comm Board.

- The 4025 Display Controller Board has provisions for obtaining dot patterns for alternate character sets from the optional Graphics Memory and Character Set Expansion Boards. Also, the 4025 Display Controller has provision for attaching connectors (Option 40) to a 4631 Hard Copy Unit and an external video monitor.

- The 4025 has provisions for adding many options: graphics, several alternate character sets, RS-232 peripheral interface, GPIB peripheral interface, etc. Fewer options are available for the 4024.

- The 4025 has a cooling fan; the 4024 does not.

#### NOTE

The following discussion assumes for convenience that the terminal is a 4025. For instance, it refers always to the "Processor" or "Processor Board," rather than to the "Processor/Comm Board." Significant differences between the two terminals are pointed out.

Figure 2-1. 4024 System Block Diagram.

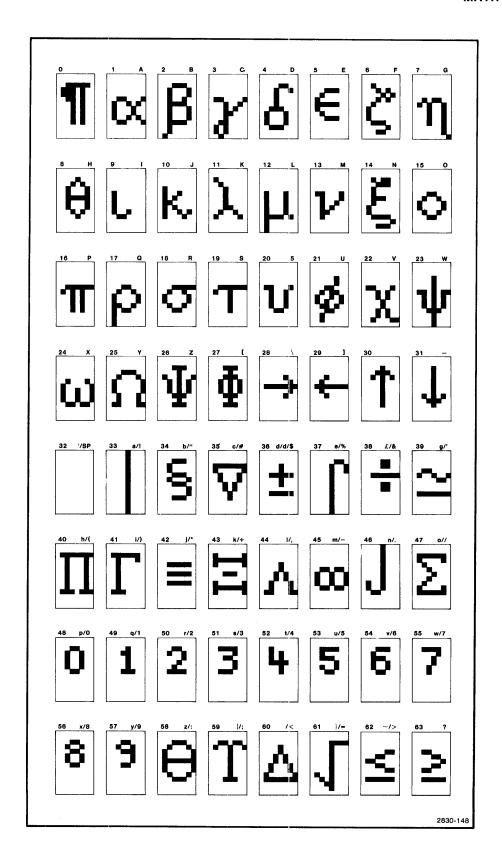

The 4024/4025 is based on an 8080 microprocessor. This device can address up to 65,536 eight-bit words of memory. Part of the memory resides on the Processor Board, but most of it is on other boards, especially the Display Memory Board.

To communicate with memory on other boards, the Processor uses certain signal lines in the Mother Board. The most important of these are the Address Bus (signal lines BAO to BA15), the Data Bus (BD0-BD7), and the READ and WRITE lines. (See the Mother Board circuit description—in Section 3 of this manual—for information on these and other Mother Board signal lines.)

Figure 2-2. 4025 System Block Diagram.

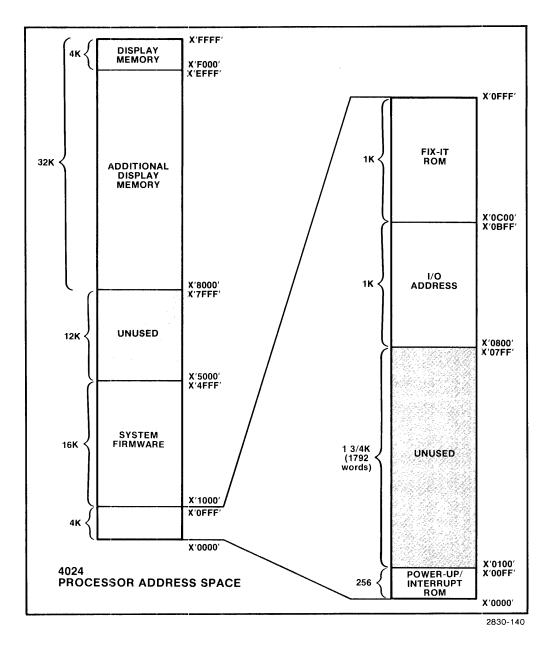

## **MEMORY ADDRESS SPACE**

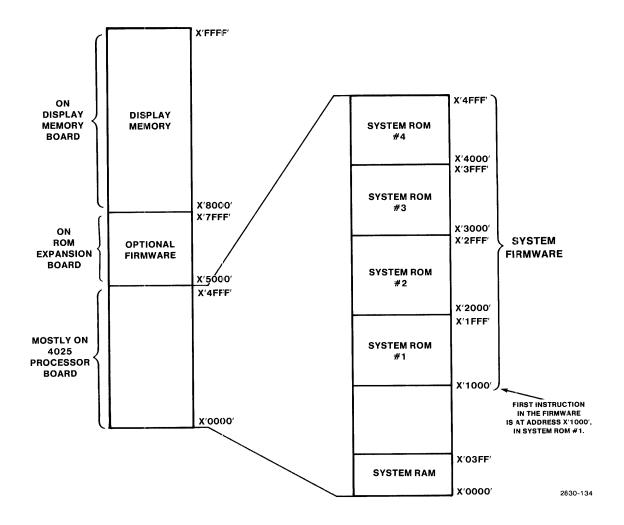

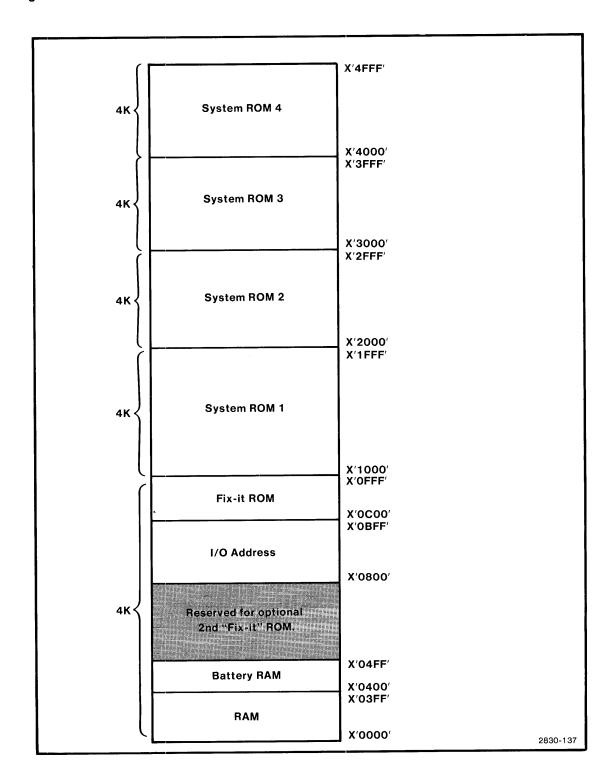

The Processor *memory address space* is the collection of all 65,536 possible memory addresses. Different parts of memory address space are used for different purposes, and some parts are not used at all. Figures 2-3 and 2-4 show the memory allocations for the 4024 and the 4025.

Figure 2-3. 4024 Memory Map.

#### SYSTEM OVERVIEW

#### System RAM

In the 4025, the lowest memory addresses (X'0000' to X'03FF') hold RAM (Random Access Memory, or read/write memory). This *System RAM* resides on the Processor Board and is used by the Processor as a scratchpad. Also, certain low-address words of memory hold "pointers" which direct the Processor to the appropriate instructions for responding to interrupt conditions.

The 4024 lacks System RAM. It uses RAM on the Display Memory Board for its scratchpad. To hold the pointers to the interrupt-handling subroutines, the 4024 uses a 256-byte ROM (addresses X'0000' to X'00FF').

#### **Battery RAM**

Memory locations X'0400' to X'04FF' are in the battery-powered RAM on the 4025's Processor Board. This RAM holds settings such as baud rate, parity, etc., so that the 4025 "remembers" the settings even when its power is turned off. (The 4024 lacks a battery-powered RAM; in the 4024, these memory locations are unused.)

#### I/O Address

Memory locations X'0800' to X'0BFF' are reserved for "I/O registers" on boards other than the Processor Board. The Processor can write to, and read from, these registers in exactly the same way as it accesses any other location in memory. Unlike other memory locations, however, the I/O registers do not store data or instructionsfothe Processor. Instead, the Processor uses them to send control signals to the other boards, or to receive signals from those boards.

For instance, by writing into memory location X'0832', the Processor can light the LEDs in the keyboard's lighted function keys; and by reading from that location, it can tell which keys are being pressed. This technique is called "memory-mapped I/O." It gives the Processor access to a wide variety of signal lines, without the need for those lines to be directly wired to the Processor.

#### Fix-It ROM

Addresses X'0C00' to X'0FFF' are reserved for the *Fix-It ROM*, a read-only memory used to make corrections to firmware. (The Fix-It is discussed later in this section.)

#### Second Fix-It ROM

Memory locations X'0800' to X'0BFF' are reserved for a Fix-It ROM, used to make changes to the optional firmware. This ROM, if installed, resides on the ROM Expansion Board.

#### **System Firmware**

Addresses X'1000' to X'4FFF' are occupied by four ROMs which hold the terminal's system firmware.

#### **Optional Firmware**

Addresses X'5000' to X'7FFF' are reserved for optional firmware ROMs. These ROMs are installed in the ROM Expansion Board.

The 4024 does not use this block of memory addresses.

## **Display Memory**

Addresses X'8000' to X'FFFF' are reserved for display memory (on the Display Memory Board). This is the terminal's main memory resource; in it are stored all the text in the workspace and monitor scrolls of memory, as well as input/output buffers, programmed key definitions, etc.

Addresses X'F000' to X'FFFF' are used for the minimum 4K of display memory. As more display memory is added, it extends downward from X'F000'. With the maximum 32K (Option 22) installed, display memory occupies addresses X'8000' to X'FFFF'.

#### HOW TEXT IS STORED AND DISPLAYED

From the user's point of view, the terminal stores text in two independent scrolls of memory: the monitor and the workspace. Parts of the two scrolls are displayed on the screen. Either the operator or the computer can insert text into either scroll.

#### **Display List**

Internally, the two scrolls are just different parts of the same *display list*. That list is a sequence of words in display memory containing all text in the monitor and workspace scrolls, together with instructions for displaying that text. To designate which parts of the display list shall appear on the screen, the Processor inserts instructions in the list.

Other circuitry automatically reads the display list, follows the instructions it contains, and generates video signals for the Video Display Unit. This circuitry consists of the Tracker (on the Display Memory Board), and the Display Controller (on its own board).

#### **Tracker**

The Tracker is a specialized processor which reads the display list and composes, line by line, information for the Display Controller. While the Display Controller scans one line of text, the Tracker is sending it the information for the next line. The Tracker communicates with the Display Controller by means of the "paired bus" lines of the Mother Board.

#### **Display Controller**

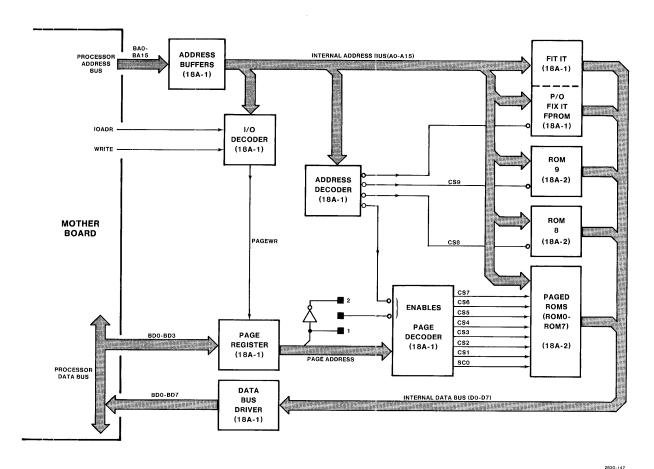

The Display Controller receives from the Tracker information about which characters to display. It consults its own Character Set Memory (not part of Processor address space) to learn how to draw those characters, and then generates signals for the Video Display Unit.

Usually, characters are displayed in character font zero (the standard font). A ROM on the Display Controller Board holds the details of how to draw characters in this font.

Sometimes, though, other fonts are used. For rulings or math characters, the Display Controller consults a ROM on the Character Set Expansion Board. (In the 4024, the rulings ROM is on the Display Controller Board.) For graphics characters, the 4025 Display Controller consults RAMs on the Graphics Memory Board. A ribbon cable carries character font information betweeen the Display Controller, Character Set Expansion and Graphics Memory Boards.

#### **Entering Text From the Keyboard**

(See Figure 2-5.)

To see the functions of the different circuit boards, let's consider what happens when the operator types text into the terminal's internal workspace. (This simplified procedure omits many details.)

- The operator types the letter "w."

- 2. The keyboard tells the Data Communications Interface that "the W key is being pressed—and the SHIFT key is not pressed."

- 3. The Communications Interface Board puts a "key pressed" code into its Keyboard Port Data Word. This is a register on the Communications Interface Board which appears to the Processor to be memory location X'0832'.

- 4. The Processor reads from location X'0832'.

- 5. The Processor decides, based on the data just read, that "lowercase w" is the character just typed. It inserts the ASCII character w in the display list at the current cursor location.

- (If "lowercase w" were programmed to mean HI MOM, the Processor would have inserted HI MOM in the display list.)

- 6. While the Processor is busy with other tasks, the Tracker reads the display list. When the Tracker comes to the line containing the newly-typed character, it sends that character, along with the rest of that line, to the Display Controller. To do this, it uses the Mother Board's paired bus lines. That way, it doesn't interfere with the Processor's use of the main terminal address and data busses.

- 7. When the Display Controller is finished scanning the previous row of text, it starts on the text row just received from the Tracker. For each character to be displayed, it looks up (in its Character Set Memory) that character's dot pattern. Using this information, it generates a VIDEO signal, and sends that signal (together with the synchronizing signals DHDRIVE and DVDRIVE) to the Video Display Unit.

- 8. In response to the VIDEO, DHDRIVE and DVDRIVE signals, the Video Display Unit displays the text on its screen, including the newly-inserted letter "w."

Figure 2-5 summarizes this process; it shows the flow of information from the keyboard to the screen.

Figure 2-5. Flow of Information from Keyboard to Screen.

#### **VIRTUAL BIT MAP GRAPHICS**

Suppose the user wants to draw graphs in an area which occupies all 80 columns of 34 lines of text. Such a graphic region includes 304,640 addressable points. The usual "bit map" method of storing this data would require 304,640 bits: 38,080 eight-bit words of memory.

To save memory, the 4025 uses a "virtual bit map" method of storing graphic information. This method takes advantage of the fact that most pictures and graphs have many blank areas.

For each 8-dot by 14-dot character position ("graphics cell"), there are two bytes in the display list. (This is the same display list that holds all the other text in the workspace and monitor scrolls of memory.) The first byte names an alternate character font, and the second byte specifies one of 128 characters in that font.

When the Tracker reads the display list, it tells the Display Controller, for each graphics cell, which character of which character font to display.

When the graphics region is first created, all its cells are "character number 32 of font number 0"—in other words, ASCII spaces. The Display Controller already knows how to display ASCII spaces, so no additional graphics memory is needed.

To draw a line in the graphics region (execute a VECTOR command), the Processor first determines through which graphics cells the line will pass. It then assigns characters of alternate character fonts to these cells, and tells the Graphics Memory Board how those characters should be drawn. (That is, it specifies which dots should be turned on in each cell's dot matrix.)

Only those character cells through which lines are drawn have their dot patterns stored on the Graphics Memory Board. Thus, a graph with few lines requires little Graphics Memory. A more complex graph, with lines passing through more graphics cells, would require more Graphics Memory.

# **Section 3**

# VIDEO DISPLAY UNIT, POWER SUPPLY, AND MOTHER BOARD

#### This section describes:

• The 4024/4025 Video Display Unit and its power supply.

#### NOTE

Theory of operation for the Video Display Unit is for all serial numbers. However, for 4024 terminals serial numbered B031219 and up and 4025 terminals serial numbered B054354 and above the partial circuit diagrams shown are only approximations. For a complete circuit diagram for these terminals, see schematic diagram 3-2 in Volume 2 of this service manual.

- The main power supply for the terminal, which is separate from the Video Display Unit's supply.

- The terminal's Mother Boards, which differ only in the number of edge connectors installed.

Figure 3-1. Video Display Unit Block Diagram.

#### VIDEO DISPLAY UNIT

The Video Display Unit's block diagram is shown in Figure 3-1. Detailed schematic diagrams are included with the circuit descriptions; however, for the most complete and accurate schematics and parts lists, see Volume 2 of this Service Manual.

The Display Unit includes the following circuits: Display Power Supply, Video Amplifier, Horizontal Sync Amplifier, Phase Detector, Horizontal Oscillator, Horizontal Pulse Shaper and Driver, Horizontal Output, Vertical Sync Amplifier, Sync Shaper, Vertical Oscillator, Vertical Driver, and Vertical Output. Each is described in turn.

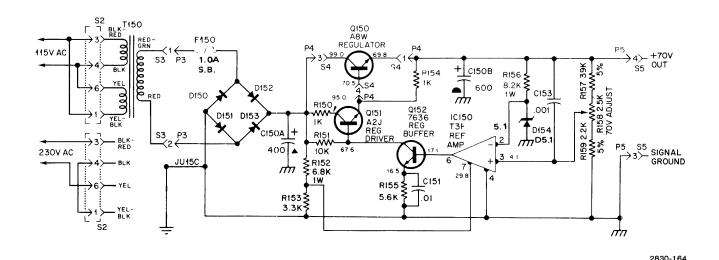

#### Display Power Supply (See Figure 3-2.)

The Power Supply is a transformer-operated, full wave, regulated series pass circuit that maintains a constant output voltage with line input variations of  $\pm$  12.5%. Depending on how connector S2 is wired, operation from 115 or 230 volts, 50/60 Hz is possible. Integrated circuit IC150 is the reference amplifier, transistor Q152 is a regulator buffer, transistor Q151 is the regulated output driver, and Q150 is the series pass transistor.

The output voltage, + 70V, appears at the emitter of Q150. This voltage is divided between R157, R158 and R159. The voltage on the arm of potentiometer R158 (70V ADJ control) is the reference input to the non-inverting input of reference amplifier IC150.

Figure 3-2. Display Power Supply.

A temperature-compensated zener diode, D154, establishes a fixed reference voltage at the inverting input to IC150. Resistor R156 provides a bias current for D154, which establishes the operating point of D154. Capacitor C153 is a high-frequency filter. Operating voltage for IC150 is derived from a voltage divider consisting of R152 and R153. Components R155 and C151 set the voltage gain of Q152.

An increase in output voltage results in an increase of voltage at the base of Q152 via the non-inverting input of IC150. The change in bias voltage turns Q152 on more, reducing its collector voltage. This reduces the forward bias to Q151, which results in less emitter current for Q150. With Q150 conducting less, the output voltage is lowered.

Dual-section capacitor C150 provides filtering.

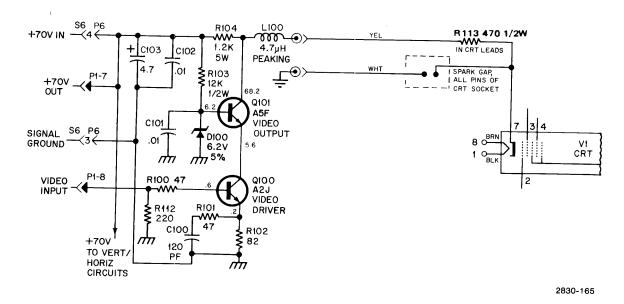

## **Video Amplifier**

(See Figure 3-3.)

The Video Amplifier consists of two stages, Q100 and Q101, connected in a cascode configuration.

A TTL compatible non-composite video signal, approximately 4.0 volts P-P, is dc coupled to the base of Q100 via R100. Resistor R112 provides proper termination for the high-frequency compensation to maintain a flat response when Q100 and Q101 conduct.

During no-signal conditions, Q100 is off. Transistor Q101, however, is forward biased by the 6.2 volts on its base, which is established by zener diode D100. When a video signal is applied to the base of Q100, it conducts, which causes forward biased Q101 to conduct. The resultant output is developed across R104 at the collector of Q101; then is dc-coupled to the cathode of V1 (CRT) via peaking coil L100 and R113. Resistor R113 isolates Q101 from transients that may occur as a result of crt arcing. Capacitor C101 shunts to ground any high frequency video that may appear on the base of Q101. Peaking coil L100 boosts the high frequencies of the video signal. Capacitor C103 provides additional filtering of the + 70V power supply lines, while C102 is a high-frequency AC bypass capacitor.

Figure 3-3. Video Amplifier.

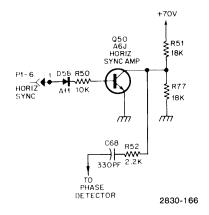

## **Horizontal Sync Amplifier**

(See Figure 3-4.)

The Horizontal Sync Amplifier consists of one stage, Q50, which operates as a switch. During a no-signal condition, Q50 is off. When a positive-going horizontal sync signal, approximately 4.0 volts P-P, is applied (dc coupled) to the base of Q50, it goes into saturation. The amplified output is developed across load resistor R51, approximately 35V, which forms a voltage divider with R77. The negative-going horizontal sync pulses are ac coupled to the phase detector circuit via the R-C network consisting of R52 and C68, a high-frequency pass filter.

Figure 3-4. Horizontal Sync Amplifier.

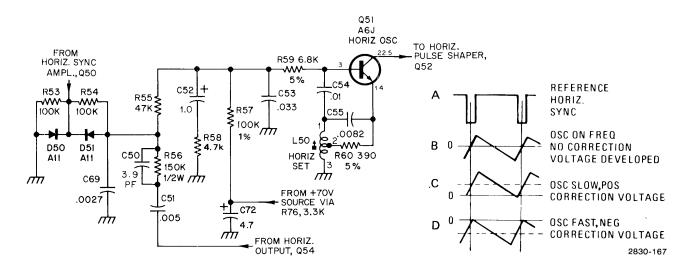

#### **Phase Detector**

(See Figure 3-5.)

The Phase Detector consists of two diodes (D50 and D51) in a keyed clamp circuit. Two inputs are required to generate the required output, one from the Horizontal Sync Amplifier, Q50, and one from the Horizontal Output circuit, Q54. The required output must be the proper polarity and amplitude to correct phase differences between the input horizontal sync pulses and the horizontal time base.

The Horizontal Output (Q54) collector pulse is integrated into a sawtooth by R56 and C69. During horizontal sync time, diodes D50 and D51 conduct, which shorts C69 to ground. This effectively clamps the sawtooth on C69 to ground at sync time. If the horizontal time base is in phase with the sync (waveform A), the sync pulse occurs when the sawtooth is passing through its AC axis and the net charge on C69 will be zero (waveform B). If the horizontal time base is lagging the sync, the sawtooth on C69 is clamped to ground at a point negative from the AC axis. This will result in a positive DC charge on C69 (waveform C). This is the correct polarity to cause the Horizontal Oscillator to speed up to correct the phase lag. Likewise, if the horizontal time base is leading the sync, the sawtooth on C69 will be clamped at a point positive from its AC axis. This results in a net negative charge on C69, which is the required polarity to slow the Horizontal Oscillator (waveform D).

Components R55, C52, R58 and C53 comprise the Phase Detector filter. The bandpass of this filter is chosen to provide correction of Horizontal Oscillator phase without ringing or hunting. Capacitor C50 times the phase detector for correct centering of the picture on the raster.

Figure 3-5. Phase Detector and Horizontal Oscillator.

#### **Horizontal Oscillator**

(See Figure 3-5.)

The Horizontal Oscillator consists of Q51, which is employed as a modified type of Hartley oscillator. The operating frequency of this oscillator is sensitive to its base input voltage. This permits control by the output of the phase detector. Resistor R57 provides DC bias to turn on Q51 and start the oscillator. The free-running horizontal frequency is adjusted with the HORIZ.SET coil, L50. This coil and capacitor C54 are the frequency determining components. Capacitor C55 and resistor R60 are feedback components for the oscillator circuit.

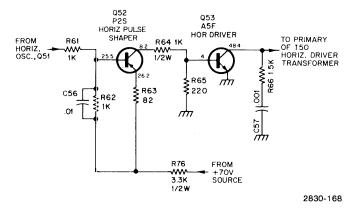

#### Horizontal Pulse Shaper and Driver

(See Figure 3-6.)

Transistor Q52 is a buffer stage between the Horizontal Oscillator and Horizontal Driver. It provides isolation for the Horizontal Oscillator as well as a low impedance drive for the Horizontal Driver. Components R62 and C56 form a time constant that shapes the oscillator output to the required duty cycle, approximately 50%, to drive the Horizontal Output circuitry.

Figure 3-6. Horizontal Pulse Shaper and Driver.

The Hozontal Driver stage, Q53, operates as a switch to drive the Horizontal Output transistor (Q54) through T50. Because of the low impedance drive and fast switching times furnished by Q52, very little power is dissipated in Q53. Components R66 and C57 provide damping to suppress ringing in the primary of T50 when Q53 goes into cutoff. (Reference Figure 3-1; Resistor R68 provides current limiting for Q53 while C58 is an ac bypass capacitor.)

# **Horizontal Output**

(See Figure 3-7.)

The secondary of T50 provides the required low drive impedance for Q54. Components R67 and C59 form a time constant for fast turn-off of the base of Q54. Once during each horizontal period, Q54 operates as a switch that connects the supply voltage across the parallel combination of the horizontal deflection yoke and the primary of the high-voltage transformer. The required sawtooth deflection current (through the horizontal yoke) is formed by the L-R time constant of the yoke and primary winding of the H.V. transformer, T51. The horizontal retrace pulse charges C62 through D54 to provide operating voltage for G2 of the crt. Momentary transients at the collector of Q54, should they occur, are limited to the voltage on C62 since D54 will conduct if the collector voltage exceeds this value.

Figure 3-7. Horizontal Output Circuit.

The damper diode, D53, conducts during the period between retrace and turn on of Q54. Capacitor C65 is the retrace tuning capacitor, while C61 blocks dc from the deflection yoke. Coil L51 is a magnetically biased linearity coil that shapes the deflection current for optimum trace linearity. Coil L53 is a series HORIZ.WIDTH control. Components R72 and C70, C64 and R75 are damping network components for the horizontal linearity (L51) and width (L53) controls. Capacitor C71 couples horizontal sync pulses from Pin 7 of T51 to diode clamp D55, which maintains the -70V reference voltage.

# **Vertical Sync Amplifier**

(See Figure 3-8.)

The Vertical Sync Amplifier consists of one stage, Q1, which operates as a switch. During no-signal conditions, Q1 is off. When a positive-going vertical sync signal, approximately 4.0 volts P-P, is applied (direct coupled) to the base, Q1 goes into saturation. The amplified output is developed across load resistor R3 to approximately 11 volts. Jumpers JU3, JU4, and JU5 are inserted, depending on the polarity of the input vertical sync pulse: TTL NEG for negative-going and TTL POS for positive-going.

Figure 3-8. Vertical Sync Amplifier and Sync Shaper.

# Sync Shaper

(See Figure 3-8.)

The negative-going vertical sync pulses (from Q1) are direct coupled to the non-inverting input of the Sync Shaper stage, IC1. The combined action of an integrating network, consisting of C1, C2, C3, R5, R6, and R7, removes high-frequency noise from the vertical sync pulses. Capacitor C3 performs the actual integrating, while resistors R5-R7 provide biasing for IC1. Capacitors C1 and C2 provide a bypass function.

#### **Vertical Oscillator**

(See Figure 3-9.)

The negative-going vertical sync pulses are ac coupled (C4) to the gate of a programmable unijunction transistor device, D1. This device turns on with each negative-going sync pulse applied to its gate. This action permits C6 and C7 to discharge very rapidly and then recharge slowly during the period that a sync pulse is not applied to the gate. The recharge path for C6 and C7 is through R12 and R13. As soon as the next sync pulse is applied to the gate of D1, C6 and C7 discharge very rapidly again. This sequence of events produces a positive-going ramp, or sawtooth waveform, at the anode of D1.

When no vertical sync pulses are connected to the monitor, Vertical Oscillator D1 is kept free-running to maintain a raster on the crt. This is accomplished by biasing the gate of D1 in conjunction with the charge and discharge action of C6 and C7. Resistors R9 and R8 provide the proper bias for D1, which also determines the repetition rate for the charge and discharge action of C6 and C7.

Figure 3-9. Vertical Oscillator/Driver.

#### **DISPLAY UNIT**

In addition, during no-signal conditions, components R22 and D2 (in conjunction with D1) provide a small incremental voltage above ground to compensate for the base-emitter voltage drop of the vertical driver, Q3. This is necessary to keep the Vertical Output stage, Q4, from being driven into cutoff, which could distort the vertical linearity.

### **Vertical Driver**

(See Figure 3-9.)

The positive-going sawtooth waveform from the anode of D1 is direct coupled to the base of Vertical Driver Q3, which operates as an emitter follower. The sharp fall time of the sawtooth is a result of the rapid discharge of C6 and C7 through D1. The amplitude of the sawtooth is varied with the HEIGHT control, R12.

The output sawtooth from the emitter of Q3 is direct coupled to the base of Vertical Output stage Q4. Part of this sawtooth waveform, however, is also coupled back to the junction of C6 and C7 via R18 and VERT.LIN control R17 for proper shaping. Since this path is resistive, the waveform is integrated into a parabola waveform by C7 (waveform A). This results in a predistortion of the drive sawtooth (waveform C). (Waveform B illustrates the drive sawtooth without parabola shaping.) Parabola shaping is necessary to compensate for the non-linear charging of C6 and C7. An additional path for phase compensation is provided through C12 and R19.

# **Vertical Output**

(See Figure 3-10.)

The positive-going sawtooth waveform from the emitter of Q3 is applied to the base of Vertical Output stage Q4, which conducts only during the ramp, or rise time, of the sawtooth waveform. The inverted ramp output (collector current) is the vertical trace period, which is ac coupled (via C14) to the vertical deflection yoke winding. The same collector current output is also applied to L1, which builds up a large electromagnetic field. This field collapses very rapidly when Q4 turns off during the retrace time of the waveform applied to the base of Q4. The back emf is in the form a high-voltage positive pulse, whose duration represents the vertical retrace period. To limit the pulse to a safe value, a varistor is connected across L1, with R26 providing damping.

Except for the vertical output stage, Q4, the vertical circuitry operates from a  $\pm$  12 volt source, which is derived from the  $\pm$  70V source. Resistor R27 drops the  $\pm$  70V source to the required  $\pm$  12V. Zener diode D3 holds the  $\pm$  12V constant while C11 provides additional filtering.

2830-172

Figure 3-10. Vertical Output Circuit.

# Dynamic Focus Adjustment (4024, B031219 and up; 4025, B054354 and up only)

Due to the geometry of the CRT, the electron beam travels a greater distance when deflected to a corner than it does to the center of the CRT screen. As a result, optimum focus is obtained at only one point. For most applications, an adequate adjustment is realized by setting the focus while viewing the screen at some point midway between the center of the screen and a corner. Still better focus can be had by modulating the focus voltage at a horizontal sweep rate. By doing so, optimum focus voltage is made variable along the horizontal axis of the CRT, and this compensates for the beam travel along this axis.

The AC component focus voltage is developed by the series resonant circuit, L52 and C63 (See Figure 3-12). This 80V P-P horizontal rate pulse is coupled from a tap on the horizontal output transformer, T51, via C67. The DC component of this voltage is set by FOCUS control R70. When the DYNAMIC FOCUS coil, L52, is set for best edge focus, a sinusoidal voltage of approximately 200V P-P is developed across C63. This DC voltage with an AC component is coupled through isolating resistor R108 to the CRT focus anode.

# TERMINAL POWER SUPPLY

The power supply (Schematic 1-1) provides dc voltages to run the plug-in circuit boards and ac voltages for the Video Display Unit and the fan. (The fan is omitted in the 4024.)

## **Primary Windings**

Main power transformer T1000 is tapped to operate on different line voltages. Its windings are in parallel on the lower voltage ranges and in series on the higher ones. Straps on a barrier strip set the unit for different mains voltages; the strap settings are described in Volume 2 of this service manual, under "Line Voltage Selection."

The fan is connected across trasformer taps 1 and 3, and the Video Display Unit's two primary windings across taps 1 and 6, and 4 and 7. Autotransformer action keeps the voltages across these taps the same, regardless of the voltage range for which the terminal is set. Thus, when changing from one line voltage range to another, it is not necessary to change connections in the Video Display Unit power supply or in the fan.

#### **Power Fail Detector**

The Power Fail Detector monitors the voltage at the secondary windings of T1000. When power fails, this voltage drops, turning off Q35 and turning on Q123, which shorts the PWDN line to ground. The low on PWDN provides an early warning that the power source has failed. This enables the Processor to disable the CMOS Battery RAM before the RAM's power source is transferred to the battery.

# +12 Volt Supply

The + 12 V supply uses voltage regulator IC U123 (a  $\mu$ A723 or equivalent). This IC has two independent parts: an error amplifier with series pass transistor, and a 7.15 V voltage reference. The difference between the voltage on the + 12 V sense line (fed to Pin 4 of the IC) and the reference voltage (Pin 5) is amplified by the IC and Q241, and used to control series pass element Q1105.

The voltage across R208 is a measure of the current being drawn from the supply. This voltage is sensed by the voltage regulator IC, which makes the series pass transistor limit the current at about 1.8 A.

SCR Q125 provides "crowbar" protection; excessive voltage on the + 12 V line fires the SCR, which shorts the + 12 V output to ground, blowing fuse F209.

# +5.1 Volt Supply

Pin 6 of U123 provides a reference voltage of 7.1 V, which is tapped down by a voltage divider. R258 in that divider is adjusted so that the voltage at its wiper is 5.1 V, the reference voltage for the + 5.1 V supply.

The error voltage (the difference between the reference voltage and the voltage on the + 5.1 V sense line) is amplified by U205, Q109, and Q1110, and used to control series pass transistor Q1112. Note that this transistor is in series with the *negative* lead of bridge rectifier CR1006.

The voltage across R1112 is a measure of the current being drawn from the supply. This voltage is amplified by Q38 and Q29 and used to bias Q110. When too much current is drawn from the supply, Q110 turns on, causing Q101 to think that the error voltage has gone positive. Consequently, Q101 and Q1110 shut down series pass transistor Q1112. This provides current limiting. R47 biases Q29, setting the current at which the supply self-limits; this should be set at 10.5 A.

Q1014 provides crowbar protection; should excessive voltage appear on the  $\pm$  5.1 V output line, Q1014 shorts that output to ground, blowing fuse F1007.

### -12 Volt Supply

The -12 V supply uses the same reference voltage as the +5.1 V supply. Currents derived from this reference voltage and from the -12 volts sense line are added at U55 non-inverting input. R45 and R46 are chosen so that when the -12 V sense line is indeed at -12 V, the junction of R45 and R46 is at 0.00 volts. Any error in the sense line voltage is amplified by U55 and Q357 and used to control series pass transistor Q1118.

The voltage across R58 and R356 is a measure of the current being drawn from the supply. If more than about 800 mA is drawn, Q55 turns on, turning off Q357 and Q1118.

### -5 Volt Supply

The -5 V sense line and the +5.1 V reference voltage are compared in U52, which controls series pass element Q53. This supply obtains its power from the -12 V supply. It is protected from excessive current by that supply's current limiting and by R56. If the -5 V supply's current exceeds 200 mA, the voltage across R56 causes the -5 V output to decrease in voltage.

# **MOTHER BOARD**

The Mother Board (Schematic 2-1) holds the 4024/4025 bus and the sockets into which other boards are inserted.

# **Signal Lines**

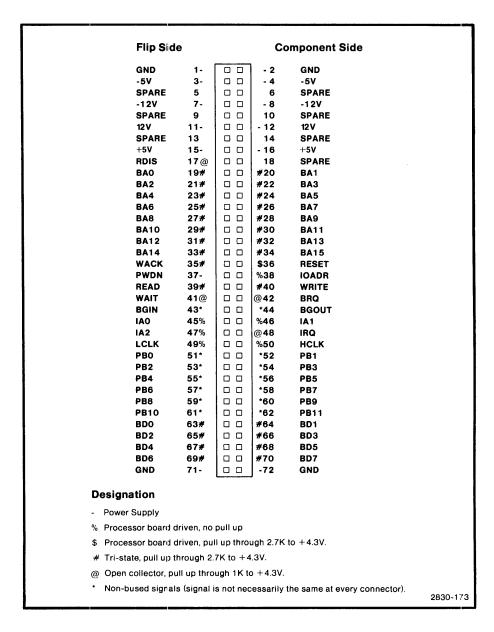

Figure 3-11 shows the connector pin identification, and Table 3-1 lists the signal lines on the Mother Board.

Figure 3-11. Bus Connector Pin Identification.

Table 3-1

# MOTHER BOARD SIGNAL LINES

| Name        | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| P/S Lines   | 1-16    | Pins 1 and 2 carry grounds. The power supply lines have spare lines interspersed between them to prevent shorts if the boards are accidentally removed or replaced with the power on.                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| RDIS        | 17      | The RDIS (ROM Disable) line is normally high. Putting this line low disables all ROMs (Read Only Memories) on the bus.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |